EMU Infos

| dumper |

f205v

|

| date |

17/04/2016

|

| emulator |

MAME 0.174

|

| dev |

Roberto Fresca

|

Technical references

CPUs

| QTY

|

Type

|

clock

|

position

|

function

|

| 1x |

PIC16C65A-20/P |

5.997 MHz |

u1 |

8bit CMOS Microcontroller (internal ROM not dumped)

|

| 1x |

D71055C |

|

u29 |

Parallel Interface Unit

|

| 1x |

Z0840006PSC-z80CPU |

5.997 MHz |

u13 |

8-bit Microprocessor - main

|

| 1x |

KA358 |

|

u4 |

Dual Operational Amplifier - sound

|

| 1x |

TDA2003 |

|

u6 |

Audio Amplifier - sound

|

| 1x |

YM2413 |

3.578 MHz |

u3 |

FM Operator Type-LL - sound

|

| 1x |

oscillator |

24.000MHz |

x2 |

|

| 1x |

oscillator |

3.579545 |

x1 |

|

ROMs

RAMs

PLDs

Others

1x 28x2 JAMMA edge connector

1x 6 legs connector(J3)

1x pushbutton(S5)

1x trimmer (volume)(PT1)

4x 8x2 switches DIP(DSW1-4)

1x 4x2 switches DIP(DSW5)

1x battery 3.6V

Notes

same layout as Champion League (v220I, dual program, set 1)

---

update 2016-05-18 from Roberto Fresca:

This set has two different programs splitted in quarters.

Both programs are intended to cover playing cards graphics (2nd quarter program), or cans (lattine) graphics to avoid some italian laws... (4th quarter program).

Seems that there's no way to switch between them. They are harcoded through the involved PLD's. Addressing lines lower than A12 are driven normally.

Main program ROM banking through PLDs...

27C2001

.-----v-----.

(VPP)-|01 32|-(VCC)

PALCE22V10H (u16) pin 21 (IO7) <---(A16)-|02 31|-(/P)

PALCE22V10H (u16) pin 05 (I4) <----(A15)-|03 30|-(A17)---> A40MX04-PL84 (u20) pin 37 (I/O)

PALCE22V10H (u16) pin 02 (I1) <----(A12)-|04 29|-(A14)---> PALCE22V10H (u16) pin 04 (I3)

RAM V62C51864 (u14) pin 03 (A7) <----(A7)-|05 28|-(A13)---> PALCE22V10H (u16) pin 03 (I2)

RAM V62C51864 (u14) pin 04 (A6) <----(A6)-|06 27|-(A8)----> RAM V62C51864 (u14) pin 25 (A8)

RAM V62C51864 (u14) pin 05 (A5) <----(A5)-|07 26|-(A9)----> RAM V62C51864 (u14) pin 24 (A9)

RAM V62C51864 (u14) pin 06 (A4) <----(A4)-|08 25|-(A11)---> RAM V62C51864 (u14) pin 23 (A11)

RAM V62C51864 (u14) pin 07 (A3) <----(A3)-|09 24|-(/G)

RAM V62C51864 (u14) pin 08 (A2) <----(A2)-|10 23|-(A10)---> RAM V62C51864 (u14) pin 21 (A10)

RAM V62C51864 (u14) pin 09 (A1) <----(A1)-|11 22|-(/E)

RAM V62C51864 (u14) pin 10 (A0) <----(A0)-|12 21|-(Q7)

(Q0)-|13 20|-(Q6)

(Q1)-|14 19|-(Q5)

(Q2)-|15 18|-(Q4)

(VSS)-|16 17|-(Q3)

'-----------'

Files

-

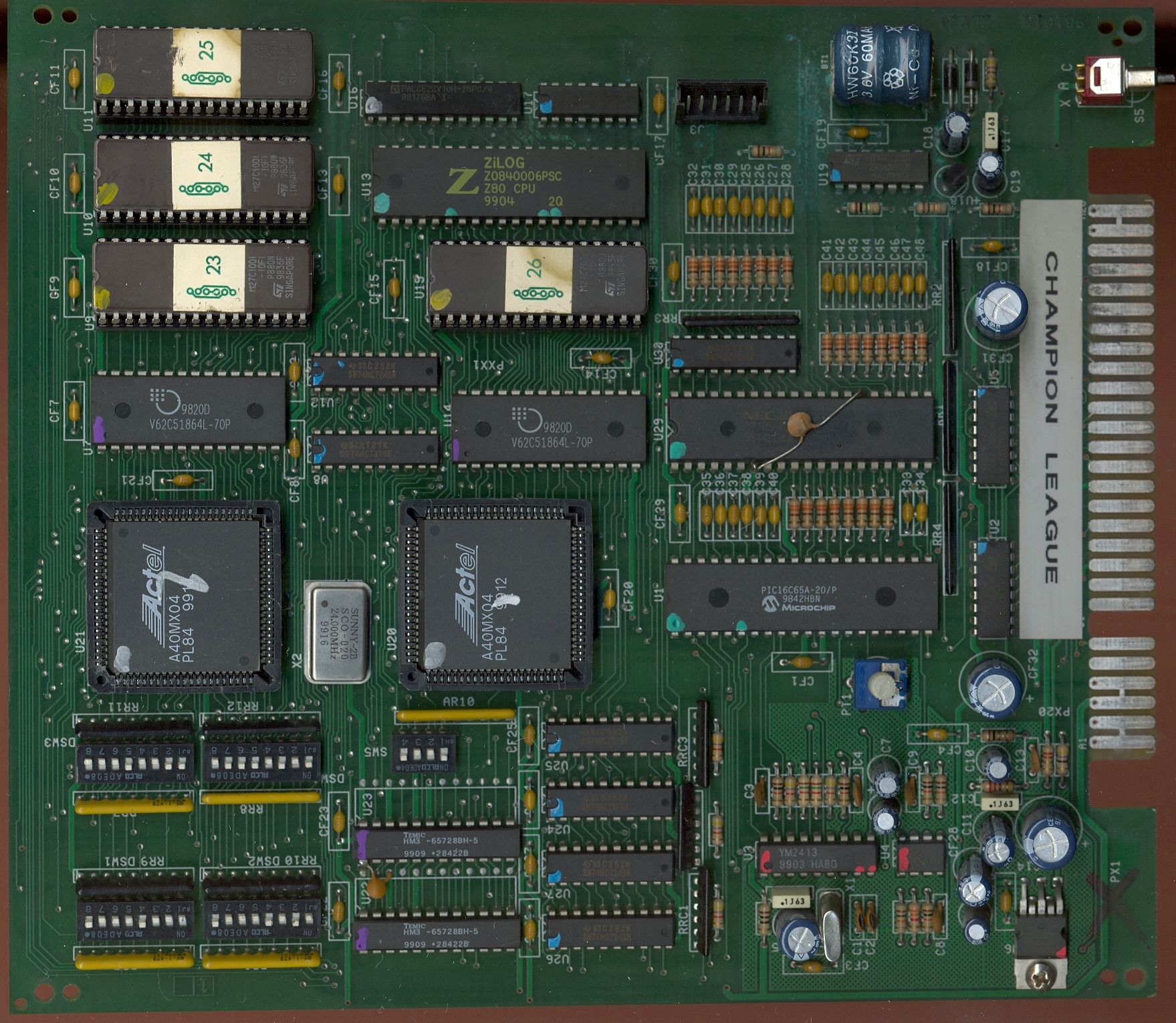

PCB component side

-

PCB solder side

1401