A40mx: Difference between revisions

From Citylan

Jump to navigationJump to search

(Created page with "'''High Density Programmable Logic''' 40MX and 42MX FPGA Families =Cross-Reference= <pre> </pre> =Pinout= <pre> LCC84 - A40MX04 +--------------------------------------------...") |

mNo edit summary |

||

| Line 1: | Line 1: | ||

'''High Density Programmable Logic''' | '''High Density Programmable Logic'''<br> | ||

40MX and 42MX FPGA Families | 40MX and 42MX FPGA Families | ||

Revision as of 17:34, 24 January 2016

High Density Programmable Logic

40MX and 42MX FPGA Families

Cross-Reference

Pinout

LCC84 - A40MX04 +---------------------------------------------------------------+ | 75 PRB-I/O | 12 NC | 33 Vcc | 54 I/O | | 76 I/O | 13 I/O | 34 I/O | 55 I/O | | 77 I/O | 14 I/O | 35 I/O | 56 I/O | | 78 I/O | 15 I/O | 36 I/O | 57 I/O | | 79 I/O | 16 I/O | 37 I/O | 58 I/O | | 80 I/O | 17 I/O | 38 I/O | 59 I/O | | 81 I/O | 18 GND | 39 I/O | 60 GND | | 82 GND | 19 GND | 40 GND | 61 GND | | 83 I/O | 20 I/O | 41 I/O | 62 I/O | | 84 I/O | 21 I/O | 42 I/O | 63 I/O | | 1 I/O | 22 I/O | 43 I/O | 64 CLK-I/O | | 2 I/O | 23 I/O | 44 I/O | 65 I/O | | 3 I/O | 24 I/O | 45 I/O | 66 MODE | | 4 Vcc | 25 Vcc | 46 Vcc | 67 Vcc | | 5 I/O | 26 Vcc | 47 I/O | 68 Vcc | | 6 I/O | 27 I/O | 48 I/O | 69 I/O | | 7 I/O | 28 I/O | 49 I/O | 70 I/O | | 8 I/O | 29 I/O | 50 I/O | 71 I/O | | 9 I/O | 30 I/O | 51 I/O | 72 SDI-I/O | | 10 I/O | 31 I/O | 52 I/O | 73 DCLK-I/O | | 11 I/O | 32 I/O | 53 I/O | 74 PRA-I/O | +---------------------------------------------------------------+

Frequency

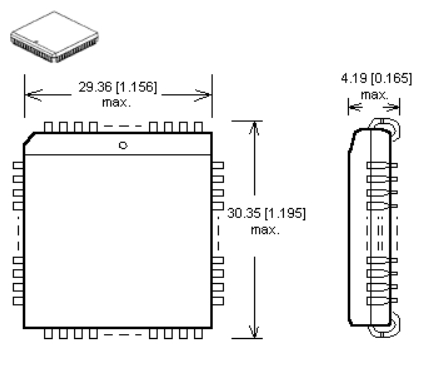

PLCC84

Set reader to FREQ, put black probe to GND, red probe to 64,73 to measure CPU clock

External links

Files

-

A40MX Datasheet