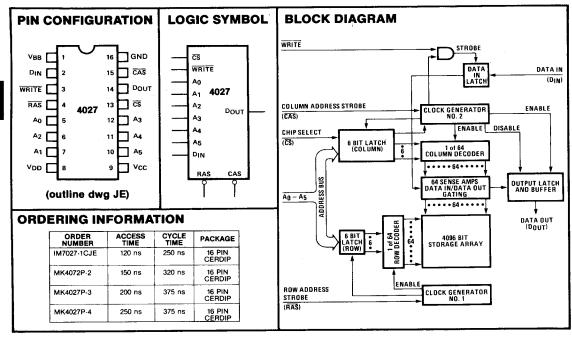

# IM7027/MK4027 Dynamic RAM 4096 Bit (4K x 1)

#### **FEATURES**

- 4096 X 1 Bit Organization

- Gated CAS

- RAS Only Refresh

- All Inputs TTL Compatible

- On-Chip Latches for Addresses, Chip Select and Data In

- 10% Supply Tolerances (+12V, +5V, -5V)

- Three-State TTL Compatible Output

- Low Power Dissipation

- -470 mW Operating

- 27 mW Standby

- Chip Select Decode Does Not Add to Access Time

- Output Data Latched and Valid Into Next Cycle

- N-Channel Silicon Gate Technology

- Pin and Performance Compatibility with Mostek MK4027

#### **GENERAL DESCRIPTION**

The IM7027 is a 4096 X 1 bit dynamic random access memory which is packaged in 16 pin DIP. The cell array is organized into 64 rows of 64 cells. Each of the 64 row addresses requires refreshing every 2 milliseconds. Any read cycle refreshes the selected row as does a refresh cycle using RAS only. A write, read/write or read/modify/write cycle also refreshes the selected row, but non-accessed chips should not be selected to avoid writing data into the selected row. A page-mode feature is included to reduce the access and/or cycle time for block data operations. Page-mode operation is useful in direct memory access (DMA) operations.

System oriented features include direct interfacing with TTL, on-chip registers which eliminate the need for interface registers, logic input levels selected for best noise immunity. Twelve address bits are required to decode 1 of 4096 cell locations, and are multiplexed onto 6 address pins and latched into the row and column address latches. The Row Address Strobe ( $\overline{RAS}$ ) latches the 6 row address bits onto the chip. The Column Address Strobe ( $\overline{CAS}$ ) latches the 6 column address bits and Chip Select ( $\overline{CS}$ ) onto the chip. Since the Chip Select signal is not required until well into the cycle, its decoding time does not add to the system address or cycle time.

## IM7027/MK4027

#### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature                      | o +70°C |

|--------------------------------------------|---------|

| Storage Temperature55°C to                 | +150°C  |

| Voltage On Any Pin w/Respect to VBB0.5V to |         |

| Power Dissipation                          | 1W      |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

#### DC CHARACTERISTICS

**TEST CONDITIONS:**  $V_{DD} = +12.0V \pm 10\%$ ,  $V_{CC} = +5.0V \pm 10\%$ ,  $V_{BB} = -5.0V \pm 10\%$ ,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$

|    | SYMBOL           | PARAMETER                                            |            | MIN  | MAX | UNITS | NOTES |

|----|------------------|------------------------------------------------------|------------|------|-----|-------|-------|

| 1  | VIHC             | RAS, CAS, WRITE Voltage High                         |            | 2.4  | 7.0 | V     |       |

| 2  | ViH              | Input Voltage High                                   |            | 2.2  | 7.0 | V     |       |

| 3  | VIL              | Input Voltage Low                                    |            | -1.0 | 0.8 | V     |       |

| 4  | link             | Input Leakage Current                                |            |      | 10  | μΑ    | 4     |

| 5  | louk             | Output Leakage Current                               |            |      | 10  | μΑ    | 5, 6  |

| 6  | I <sub>DD1</sub> | Average V <sub>DD</sub> Power Supply Current         |            |      | 35  | mA    | 2     |

| 7  | ¹cc              | V <sub>CC</sub> Power Supply Current                 |            |      |     |       | 3     |

| 8  | IBB              | Average VBB Power Supply Current                     | -2, -3, -4 |      | 300 | μΑ    |       |

|    |                  |                                                      | -1         |      | 400 | μΑ    | Ī     |

| 9  | I <sub>DD2</sub> | Standby VDD Power Supply Current                     |            |      | 2   | mA    | 5 -   |

| 10 | I <sub>DD3</sub> | Average V <sub>DD</sub> Current ("RAS Only" Refresh) |            |      | 25  | mA    |       |

| 11 | VOH              | Output Voltage High IOH = -5 mA                      |            | 2.4  |     | V     |       |

| 12 | VOL              | Output Voltage Low IOL = 3.2 mA                      |            |      | 0.4 | V     |       |

NOTES: 1. VBB must be applied before and removed after other supply voltages.

- 2. IDD1 (max) measured at <sup>t</sup>RC (min). IDD1 is proportional to cycle rate.

- 3. ICC depends on output loading.

- 4. All pins except  $V_{BB}$  at 0V,  $V_{BB} = -5V$  and test pin = +10V.

- 5. Output disabled,  $\overline{RAS}$  and  $\overline{CAS} \geqslant V_{IHC}$  (min).

- 6.  $0V \leq V_{OUT} \leq +10V$ .

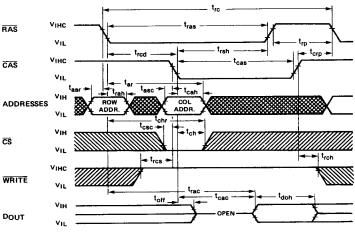

#### **TIMING DIAGRAMS**

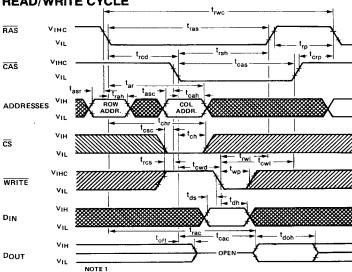

#### **READ AND REFRESH CYCLE**

8-199

8

ADDRESSES VIH ROW ADDRESS VOH

VOL

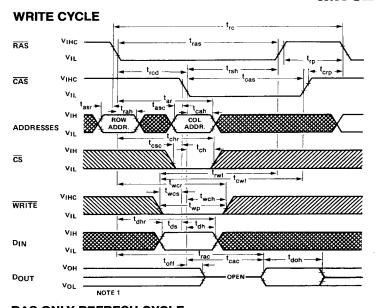

READ/WRITE CYCLE

8-200

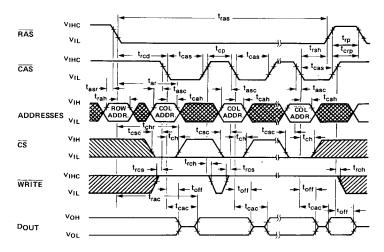

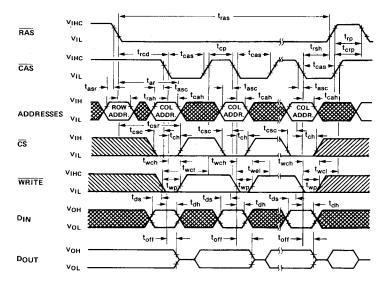

#### PAGE MODE READ CYCLE

#### PAGE MODE WRITE CYCLE

8

#### **AC CHARACTERISTICS**

TEST CONDITIONS:  $V_{DD}$  = +12.0V ± 10%,  $V_{CC}$  = +5.0V ± 10%,  $V_{SS}$  = 0V,  $V_{BB}$  = -5.0V ± 10%,  $T_{A}$  = 0°C to +70°C (NOTES 1, 5 and 8)

|    | SYMBOL            | PARAMETER                                  |     | IM7027-1CJE |     | 027 P-2 | MK4027 P-3 |               | MK4027 P-4 |        |       |          |

|----|-------------------|--------------------------------------------|-----|-------------|-----|---------|------------|---------------|------------|--------|-------|----------|

|    | TANAMETER         |                                            | MAX | MIN         | MAX | MIN     | MAX        | MIN           | MAX        | UNITS  | NOTES |          |

| 1  | t <sub>rc</sub>   | Random Read or Write Cycle Time            | 250 |             | 320 |         | 375        |               | 375        |        | ns    | 2        |

| 2  | trwc              | Read Write Cycle Time                      | 325 |             | 330 | 1       | 420        |               | 480        |        | ns    |          |

| 3  | t <sub>rac</sub>  | Access Time from Row Address Strobe        |     | 120         |     | 150     | T          | 200           |            | 250    | ns    | 3        |

| 4  | tcac              | Access Time from Column Address Strobe     |     | 80          |     | 100     |            | 135           |            | 165    | ns    | 3        |

| 5  | t <sub>off</sub>  | Output Buffer Turn-off Delay               |     | 40          |     | 40      |            | 50            | _          | 60     | ns    |          |

| 6  | t <sub>rp</sub>   | Row Address Strobe Precharge Time          | 80  |             | 100 |         | 120        |               | 120        |        | ns    |          |

| 7  | t <sub>ras</sub>  | Row Address Strobe Pulse Width             | 120 | 10,000      | 150 | 10,000  | 200        | 10,000        | 250        | 10,000 | ns    |          |

| 8  | t <sub>rsh</sub>  | Row Address Strobe Hold Time               | 80  |             | 100 |         | 135        |               | 165        |        | ns    |          |

| 9  | t <sub>cas</sub>  | Column Address Strobe Pulse Width          | 80  |             | 100 |         | 135        |               | 165        |        | ns    |          |

| 10 | t <sub>red</sub>  | Row to Column Strobe Delay                 | 20  | 40          | 20  | 50      | 25         | 65            | 35         | 85     | ns    | 4        |

| 11 | tasr              | Row Address Set-up Time                    | 0   |             | 0   |         | 0          |               | 0          |        | ns    |          |

| 12 | t <sub>rah</sub>  | Row Address Hold Time                      | 20  |             | 20  |         | 25         |               | 35         |        | ns    |          |

| 13 | tasc              | Column Address Set-up Time                 | 0   |             | -10 |         | -10        |               | -10        |        | ns    |          |

| 14 | t <sub>cah</sub>  | Column Address Hold Time                   | 45  |             | 45  | İ       | 55         |               | 75         |        | ns    |          |

| 15 | t <sub>ar</sub>   | Column Address Hold Time Referenced to RAS | 95  |             | 95  |         | 120        |               | 160        |        | ns    | -        |

| 16 | t <sub>csc</sub>  | Chip Select Set-up Time                    | -10 |             | -10 |         | ~10        | -             | -10        |        | ns    |          |

| 17 | t <sub>ch</sub>   | Chip Select Hold Time                      | 45  |             | 45  | l       | 55         |               | 75         |        | ns    |          |

| 18 | t <sub>chr</sub>  | Chip Select Hold Time Referenced to RAS    | 95  |             | 95  |         | 120        |               | 160        |        | ns    |          |

| 19 | t <sub>t</sub>    | Transition Time (Rise and Fall)            | 3   | 35          | 3   | 35      | 3          | 50            | 3          | 50     | ns    |          |

| 20 | t <sub>ros</sub>  | Read Command Set-up Time                   | 0   |             | 0   |         | 0          |               | 0          |        | ns    |          |

| 21 | t <sub>rch</sub>  | Read Command Hold Time                     | 0   |             | 0   |         | 0          |               | -          |        | ns    | +        |

| 22 | twch              | Write Command Hold Time                    | 45  |             | 45  |         | 55         |               | 75         |        | ns    |          |

| 23 | twer              | Write Command Hold Time Referenced to RAS  | 95  |             | 95  |         | 120        |               | 160        |        | ns    |          |

| 24 | twp               | Write Command Pulse Width                  | 45  |             | 45  |         | 55         | -             | 75         |        | ns    |          |

| 25 | trwi              | Write Command to Row Strobe Lead Time      | 50  |             | 50  |         | 70         |               | 85         |        | ns    |          |

| 26 | t <sub>cwl</sub>  | Write Command to Column Strobe Lead Time   | 50  | ··-         | 50  |         | 70         |               | 85         |        | ns    |          |

| 27 | t <sub>ds</sub>   | Data in Set-up Time                        | 0   |             | 0   |         | 0          |               | 0          |        | ns    | 7        |

| 28 | t <sub>dh</sub>   | Data in Hold Time                          | 45  |             | 45  |         | 55         |               | 75         | +      | ns    | 7        |

| 29 | t <sub>dhr</sub>  | Data in Hold Time Referenced to RAS        | 95  |             | 95  |         | 120        |               | 160        |        | ns    |          |

| 30 | t <sub>crp</sub>  | Column to Row Strobe Precharge Time        | 0   |             | 0   |         | 0          |               | 0          |        | ns    |          |

| 31 | t <sub>cp</sub>   | Column Precharge Time                      | 60  |             | 60  |         | 80         |               | 110        |        | ns    |          |

| 32 | t <sub>rfsh</sub> | Refresh Period                             |     | 2           |     | 2       |            | 2             |            | 2      | ms    |          |

| 33 | twcs.             | Write Command Set-up Time                  | 0   |             | 0   |         | 0          | <del>  </del> | 0          |        | ns    | 6        |

| 34 | tcwd              | CAS to WRITE Delay                         | 60  |             | 60  |         | 80         |               | 90         |        | ns    | 6        |

| 35 | t <sub>rwd</sub>  | RAS to WRITE Delay                         | 110 |             | 110 |         | 145        |               | 175        |        | ns    | 6        |

| 36 | t <sub>doh</sub>  | Data Out Hold Time                         | 10  |             | 10  |         | 10         |               | 10         |        | ns    | $\dashv$ |

NOTES 1: t<sub>t</sub> = 5 ns unless otherwise noted.

2: t<sub>rc</sub> > t<sub>ras</sub> + t<sub>rp</sub> + 2 t<sub>t</sub> 3: Load = 2TTL + 100 pF. to limit power dissipation.

- 3: Load = 2 TTL + 100 pF.

4: If ¹fed is greater than ¹fed (max) access time is controlled by ¹feac.

5: Vihc (min), Vih (min) and Vii (max) are reference levels.

6: ¹test of the standard red and ¹fred are not restrictive parameters, they are electrical characteristics only as follows:

a. ¹fewd + ¹test of the standard red is the standard - 7: Referenced to latest of CAS or WRITE.

- 8: Any 8 cycles that perform refresh are required after power is applied.

8-202

# IM7027/MK4027

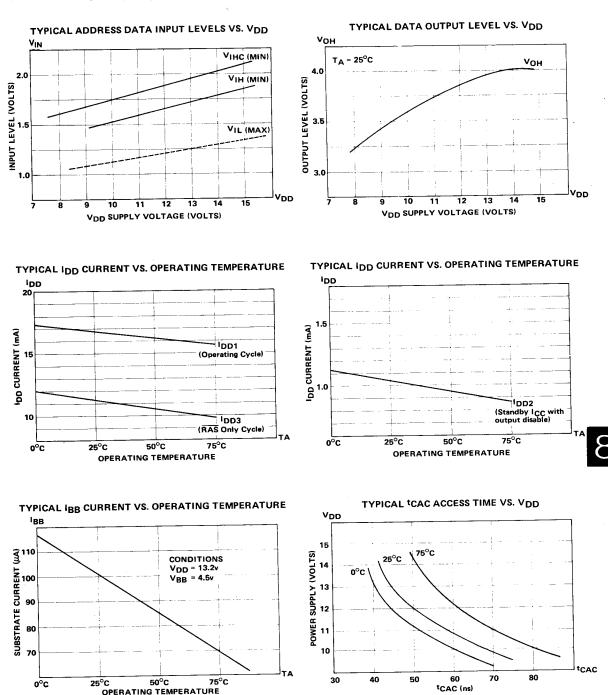

# TYPICAL DEVICE CHARACTERISTICS

8-203

This Material Copyrighted By Its Respective Manufacturer

## TYPICAL DEVICE CHARACTERISTICS (Continued)

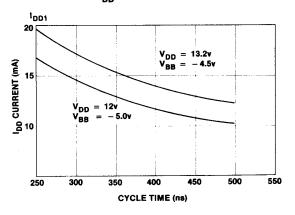

## TYPICAL IDD CURRENT VS. CYCLE TIME

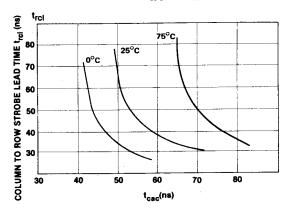

## TYPICAL t<sub>cac</sub> VS. t<sub>rcl</sub>

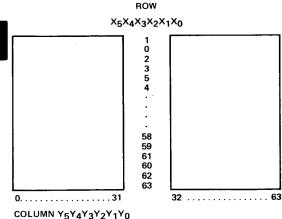

#### **BIT MAP**

The memory cells are divided into 2 groups each organized as 64 rows by 32 columns. The column addresses run in pure binary order for  $Y_5$   $Y_4$   $Y_3$   $Y_2$   $Y_1$   $Y_0$ , where  $Y_5$  is most significant. The row addresses run in binary order for  $X_5$   $X_4$   $X_3$   $X_2$   $X_1$   $X_0$  except for  $X_1$  and  $X_0$  which run 1, 0, 2, 3 and repeat. The folded bit line approach requires that data be be stored either true or false depending on the row selected. If  $X_0$  is at logic "0", data is stored true. If  $X_0$  is at logic "1", data is stored false.

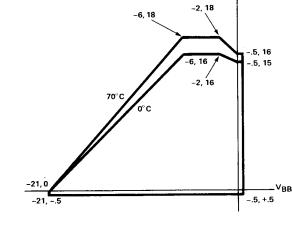

#### **MAXIMUM STRESS VOLTAGES**

It is of interest to know worst case stress voltages for power supply failure and/or turn-on conditions. The 7027 can tolerate combinations of  $V_{BB}$ ,  $V_{DD}$  that operate within the curves of the figure shown below.

$v_{DD}$

#### CAPACITANCE

TEST CONDITIONS: VIN = OV, f = 1 MHz (NOTE 1)

|   | SYMBOL          | PARAMETER                                                                 | TYP | MAX | UNIT |

|---|-----------------|---------------------------------------------------------------------------|-----|-----|------|

| 1 | C <sub>I1</sub> | D <sub>IN</sub> , CS Input Capacitance<br>A <sub>0</sub> - A <sub>5</sub> | 3   | 5   |      |

| 2 | C <sub>12</sub> | Input Capacitance, RAS, CAS<br>WRITE                                      | 5   | 7   | рF   |

| 3 | C <sub>0</sub>  | Output Capacitance, DOUT                                                  | 5   | 7   |      |

NOTE 1: These parameters are characterized and periodically sampled but not 100% tested.

8-204