# CXK27C1001DQ -15/20

# 131072-word $\times$ 8-bit Ultraviolet Erasable CMOS EPROM

### Description

The CXK27C1001DQ is an electrically programmable, ultraviolet erasable CMOS EPROM. The adoption of CMOS for the peripheral circuits allows for high speed operation and low power consumption. Ideally suited for 8-bit microprocessor systems requiring large program memories, this IC is organized as 131072-word by 8-bit in a 32 pin Frit-Seal package.

#### **Features**

- Fast access time: (Access time) CXK27C1001DQ-15 150ns (Max.) CXK27C1001DQ-20 200ns (Max.)

- Low current consumption at operation current 50mA (Max.) at standby 1mA (Max.)

- At read out 5V single supply operation: 5V ± 10 %

- Directory TTL compatible : All inputs and outputs

- 3-state output

- High speed program mode

- 600-mil 32 pin ceramic DIP package

#### **Function**

131072-word × 8-bit EPROM

#### Structure

Silicon Stacked-gate CMOS IC

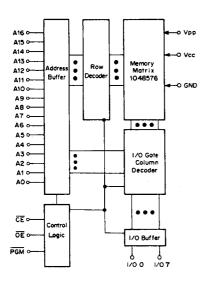

#### **Block Diagram**

# Pin Configuration (Top View)

| Pin Description |                      |  |  |  |  |

|-----------------|----------------------|--|--|--|--|

| Symbol          | Description          |  |  |  |  |

| A0 to<br>A16    | Address input        |  |  |  |  |

| I/00 to<br>I/07 | Data I/O             |  |  |  |  |

| CE              | Chip enable input    |  |  |  |  |

| ŌĒ              | Output enable input  |  |  |  |  |

| PGM             | Program enable input |  |  |  |  |

| Vpp             | Program power supply |  |  |  |  |

| Vcc             | +5V power supply     |  |  |  |  |

| GND             | GND                  |  |  |  |  |

| NC              | No connection        |  |  |  |  |

E89X10 - ST

Absolute Maximum Ratings

(Ta = 25 °C, GND = 0V)

| Item                  | Symbol            | Ratings        | Unit |

|-----------------------|-------------------|----------------|------|

| Supply voltage        | Vcc               | -0.6 to +7.0   | V    |

|                       | Vpp               | -0.6 to +14    | V    |

| Input voltage         | A9                | -0.6 to +13.5  | V    |

|                       | Vin               | - 0.6 to + 6.5 | V    |

| Output voltage        | V <sub>I</sub> /o | -0.6 to +6.5   | ٧    |

| Operating temperature | Topr              | -10 to +80     | ဗင   |

| Storage temperature   | Tstg              | -65 to +125    | ొ    |

Exposure to stress exceeding the Absolute Maximum Ratings may not only adversely affect reliability but at the worst, destroy the device.

# Truth Table

| CE | ŌĒ | A9 | PGM | Vpp | Mode                 | I/O pin            |

|----|----|----|-----|-----|----------------------|--------------------|

| L  | L  | Х  | Х   | Vcc | Read                 | Data output        |

| L  | Н  | Х  | Х   | Vcc | Output disable       | High impedance     |

| Н  | Х  | Х  | Х   | Vcc | Standby              | High impedance     |

| L  | Х  | X  | L   | Vpp | Program              | Data input         |

| L  | L  | Х  | Н   | Vpp | Program verify       | Data output        |

| Н  | Х  | Х  | Х   | Vpp | Program inhibit      | High impedance     |

| L  | L  | Vн | Н   | Vcc | Electronic signature | Device code output |

Set X to either "H" or "L",  $V_H = 12V \pm 0.5V$

# Read Mode

# Recommended Operating Conditions

(Ta = 0 to + 70 °C, GND = 0V, Vpp = Vcc\*)

|                    |        |       | •    |           |      |

|--------------------|--------|-------|------|-----------|------|

| Item               | Symbol | Min.  | Тур. | Max.      | Unit |

| Supply voltage     | Vcc    | 4.5   | 5.0  | 5.5       | ٧    |

| Input high voltage | ViH    | 2.0   |      | Vcc + 0.5 | ٧    |

| input low voltage  | VIL    | - 0.1 |      | 0.8       | V    |

<sup>\*</sup> Vpp must be applied simultaneously or after Vcc and removed simultaneously or before Vcc.

# **Electrical Characteristics**

# • DC characteristics

$(Vcc = 5V \pm 10 \%, Vpp = Vcc, GND = 0V, Ta = 0 to + 70 °C)$

| Item                                 | Symbol           | Test conditions                                                 | Min. | Тур.* | Max. | Unit |

|--------------------------------------|------------------|-----------------------------------------------------------------|------|-------|------|------|

| Input leakage current                | lu l             | V <sub>IN</sub> = 5.5V                                          | - 10 | _     | 10   | μΑ   |

| Output leakage current               | ILO              | V <sub>1</sub> ∕0 = 5.5V                                        | - 10 | Ī     | 10   | μΑ   |

| Vcc average operating supply current | lcc1             | Cycle time 125ns<br>Duty = 100 %<br>louT = 0mA<br>CE = OE = VIL |      |       | 50   | mA   |

| Vcc standby supply current           | Isa              | CE = ViH                                                        |      |       | 1    | mA   |

| Vpp supply current                   | lpp <sub>1</sub> |                                                                 |      |       | 0.1  | mA   |

| Output high voltage                  | Voн              | I <sub>OH</sub> = - 400 μA                                      | 2.4  |       |      | ٧    |

| Output low voltage                   | VoL              | ioL = 2.1 mA                                                    |      |       | 0.45 | ٧    |

<sup>\*</sup> Vcc = 5V, Ta = 25 ℃

# I/O capacitance

$(Ta = 25 \, ^{\circ}C, f = 1 \, MHz)$

| Item              | Symbol | Conditions             | Min. | Тур. | Max. | Unit |

|-------------------|--------|------------------------|------|------|------|------|

| Input capacitance | Cin    | $V_{IN} = 0V$          |      | 4    | 6    | pF   |

| I/O capacitance   | Cı/o   | V <sub>I</sub> ∕0 = 0V |      | 8    | 12   | pF   |

Note) This parameter is sampled and is not 100% tested.

# **AC** characteristics

# • AC test conditions

$(Vcc = 5V \pm 10 \%, Vpp = Vcc, Ta = 0 to + 70 °C)$

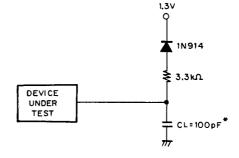

| Item                     | Conditions              |

|--------------------------|-------------------------|

| Input pulse high voltage | V <sub>IH</sub> = 2.4V  |

| Input pulse low voltage  | V <sub>IL</sub> = 0.45V |

| Input rise time          | tr ≦ 20ns               |

| Input fall time          | tf ≦ 20ns               |

| Input reference level    | 2V/0.8V                 |

| Output reference level   | 2V/0.8V                 |

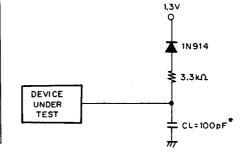

| Load condition           | Right figure            |

<sup>\*</sup> CL includes scope and jig capacitances.

| ltem                      | Symbol            | _    | - 15 |      | - 20 |      |

|---------------------------|-------------------|------|------|------|------|------|

| No                        | Gymbol            | Min. | Max. | Min. | Max. | Unit |

| Address access time       | TACC              |      | 150  |      | 200  | ns   |

| Chip enable access time   | tce               | _    | 150  |      | 200  | ns   |

| Output enable access time | toE               |      | 65   |      | 70   | ns   |

| Output data hold time     | tон               | 0    |      | 0    |      | ns   |

| Output disable time       | t <sub>DF</sub> * | 0    | 50   | 0    | 60   | ns   |

<sup>\*</sup> tor is defined by the time required by the output to reach high impedance. It is not determined by the output voltage level. This parameter is only sampled and is not 100% tested.

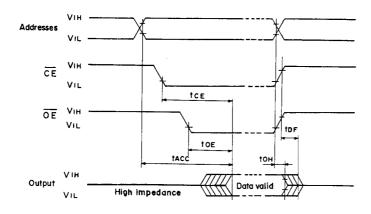

# Timing Waveform (Read cycle)

# Programming Operation

# **Recommended Operating Conditions**

$(Ta = 25 \pm 5 \,^{\circ}\text{C}, GND = 0V)$

| Item                       | Symbol | Min.  | Тур.  | Max.       | Unit |

|----------------------------|--------|-------|-------|------------|------|

| Vcc supply voltage         | Vcc*1  | 6.00  | 6.25  | 6.50       | ٧    |

| Vpp program supply voltage | Vpp*2  | 12.50 | 12.75 | 13.00      | V    |

| Input high voltage         | ViH    | 2.0   |       | Vcc + 0.5V | ٧    |

| Input low voltage          | VIL    | - 0.1 |       | 0.8        | ٧    |

- \*1 Vcc must be applied before Vpp and removed after Vpp.

- \*2 Keep Vpp below 14V including overshoot. Extraction of the device while 12.75V is applied to Vpp may impair reliability.

#### **Electrical Characteristics**

# • DC characteristics

| ltem                            | Symbol | Conditions               | Min. | Тур. | Max. | Unit |

|---------------------------------|--------|--------------------------|------|------|------|------|

| Input leakage current           | lu     | VIN = VIL OF VIH         | - 10 |      | 10   | μА   |

| Vcc supply current              | Icc2   |                          |      |      | 50   | mA   |

| Vpp supply current              | lpp2   | CE = VIL                 |      |      | 50   | mA   |

| Output high voltage (at verify) | Voн    | Іон = - 400 μΑ           | 2.4  |      |      | ٧    |

| Output low voltage (at verify)  | Vol    | I <sub>OL</sub> = 2.1 mA |      |      | 0.45 | ٧    |

| A9 electronic signature         | VID    |                          | 11.5 | 12.0 | 12.5 | ٧    |

# **AC Characteristics**

#### • AC test conditions

$(Vcc = 6.25 \pm 0.25V, Vpp = 12.75 \pm 0.25V, Ta = 20 to + 30 ^{\circ}C)$

| Item                     | Conditions              |

|--------------------------|-------------------------|

| Input pulse high voltage | V <sub>IH</sub> = 2.4V  |

| Input pulse low voltage  | V <sub>IL</sub> = 0.45V |

| Input rise time          | tr≦20ns                 |

| Input fall time          | tf ≦ 20ns               |

| Input reference level    | 2V/0.8V                 |

| Output reference level   | 2V/0.8V                 |

| Load conditions          | Right figure            |

<sup>\*</sup> CL includes scope and jig capacitances.

| Item                          | Symbol | Min. | Max. | Unit |

|-------------------------------|--------|------|------|------|

| Address setup time            | tas    | 2    |      | μs   |

| OE setup time                 | toes   | 2    |      | μs   |

| Data setup time               | tos    | 2.   |      | μs   |

| Address hold time             | tah    | 0    |      | μs   |

| Data hold time                | ton    | 2    |      | μs   |

| OE high to output float delay | tDFP*  | 0    | 130  | ns   |

| Vpp setup time                | tvps   | 2    |      | μs   |

| Vcc setup time                | tvcs   | 2    |      | μs   |

| CE setup time                 | tces   | 2    |      | μs   |

| Program pulse width           | tpw    | 95   | 105  | μs   |

| Data valid from OE            | toE    |      | 100  | ns   |

<sup>\*</sup> topp is defined by the time required by the output to reach high impedance. It is not determined by the output voltage level. This parameter is only sampled and is not 100% tested.

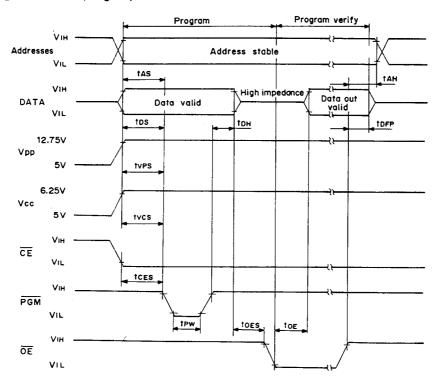

# Timing Waveform (Program)

Note) When programming the CXK27C1001DQ a  $0.1\,\mu\text{F}$  capacitor is required access Vpp and GND to suppress switching noise caused by Vpp transient current.

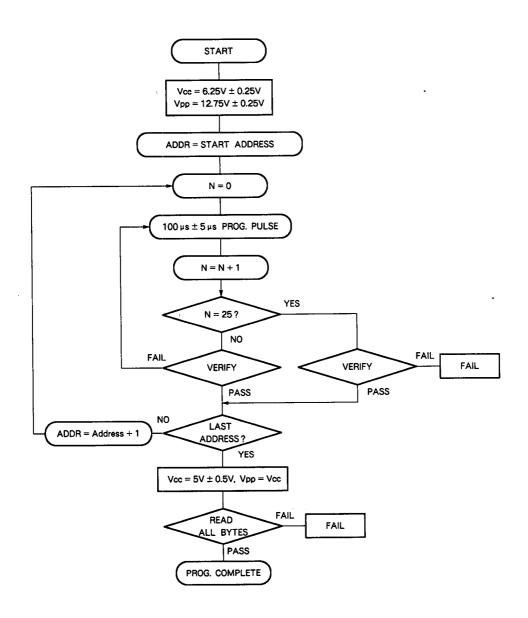

High Speed Programming Method Flow Chart Flowchart

# Erasure Operation

The recommended erasure procedure for the CXK27C1001DQ ("0" to "1") is exposure to ultraviolet light of a 2537 Å wavelength through the translucent window. The exposure dose (i.e. UV intensity X exposure time) for erasure should be at a minimum of 15W-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with an illuminance of  $12000\,\mu\text{W}/\text{cm}^2$  on the package surface placed within 2 to 3cm of the lamp tubes. Moreover, erasure may require larger periods according to the ultraviolet lamp life and the dirt on the quartz window.

In this IC, erasure of data starts when exposed to light with a wavelength of 4000 Å or less. Considering that sunlight and some fluorescent lighting contain elements of a wavelength between 3000 and 4000 Å, long usage under such type of lighting conditions calls for protection. In such cases, use an opaque seal and the like to cover the glass window and prevent chip exposure to light.

#### **Operation Modes**

#### Read Mode

This IC features a chip enable  $(\overline{CE})$  and an output enable  $(\overline{OE})$ .  $\overline{CE}$  selects the device and at the same time controls the power down function.  $\overline{OE}$  controls the output buffer, independently from  $\overline{CE}$ . By setting the address while  $\overline{CE} = \overline{OE} = V_{1L}$ , data becomes stable after tacc.

After address has become stable, respective data become stable when after tce,  $\overline{CE}$  is lowered to  $V_{IL}$  from  $V_{IH}$  in  $\overline{OE} = V_{IL}$  condition, or  $\overline{OE}$  is lowered from  $V_{IH}$  to  $V_{IL}$  in  $\overline{CE} = V_{IL}$  condition, after toe.

#### **Output Disable Mode**

By turning  $\overline{\text{OE}}$  to V<sub>IH</sub>, the output pin turns to high impedance condition irrespectively of other inputs. This function completely prevents bus contention and allows for an easy connection of several devices on a common bus line.

#### Standby Mode

Turning  $\overline{CE}$  to V<sub>IH</sub> automatically brings in power down condition. Then consumption current lcc is reduced to a maximum 1mA. Also, output turns to high impedance condition irrespectively of  $\overline{OE}$ .

#### Notes on Operation

Supply current lcc features 3 levels depending on the device operating condition. Standby current level, operating current level and transient peak current level. The transient peak current is the source of switching noise and the cause of high speed IC's misoperation. As the magnitude of the transient peak current heavily depends on the inductance and capacitance of the output load. This can be suppressed through the usage of a decoupling capacitor.

When the system is built, it is recommended to insert a high frequency 1  $\mu$ F ceramic capacitor between Vcc and GND on every device, and as close to the device as possible.

In addition, a 4.7 µF electrolytic capacitor is recommended for every 8 devices. This should be close to the power supply to overcome voltage drop caused by the PCB wiring inductance.

#### Program Mode

When delivered, and after each erasure, all bits of the CXK27C1001DQ are in the "1" state (Output "H" level). Data is introduced by selectively programming "0s" (output "L" level). To change a "0" to a "1" by ultraviolet light erasure is necessary. (See article on UV Erasure.) The CXK27C1001DQ is set to programming mode when 12.75V is applied to Vpp pin and "L" level to  $\overline{\text{CE}}$  and  $\overline{\text{PGM}}$ .

#### High Speed Programming Method

During programming and verify operation a circuit that automatically monitors the programming of cells is activated. Thus over program pulse so far in use is not necessary, and programming time is greatly reduced to 13 seconds.

#### Program Inhibit Mode

By turning Vpp to 12.75V and  $\overline{\text{CE}}$  to V<sub>IH</sub>, programming is inhibited. Using this method allows for programming of multiple devices in parallel with different data. With the exception of  $\overline{\text{CE}}$  wiring is common. With the input of  $\overline{\text{CE}} = \text{V}_{\text{IL}}$  pulse into the device selected for programming, this can be performed independently from other devices.

#### **Program Verify**

To verify if programming has been correctly performed at the specified address, memory cells are read out. Data of the selected address is output by turning to  $\overline{CE} = \overline{OE} = V_{IL}$ , and  $\overline{PGM} = V_{IH}$  at Vpp = 12.75V.

#### Electronic Signature Mode

Electronic signature serves to identify the manufacturer and the device type of each EPROM. This function is intended for use by the programming equipment to automatically match the device to be programmed with its corresponding programming algorithm.

At read mode, 12V is applied to address A9.

At to As, Ato to At6 =  $\overline{OE} = \overline{CE} = V_{IL}$  and  $\overline{PGM} = V_{IH}$  is obtained.

With  $A_0 = V_{IL}$  the manufacturer code is output and with  $A_0 = V_{IH}$  the device code is output. The chart below shows the Electronic Signature.

| Pins<br>Signature | Α0  | 07 | 06 | 05 | 04 | 03 | 02  | 01 | 00 | Hex |

|-------------------|-----|----|----|----|----|----|-----|----|----|-----|

| Manufacturer Code | VIL | 0  | 0  | 1  | 0  | 0  | - 0 | 0  | 0  | 20  |

| Device Code       | ViH | 0  | 0  | 0  | 0  | 0  | 1   | 0  | 1  | 05  |

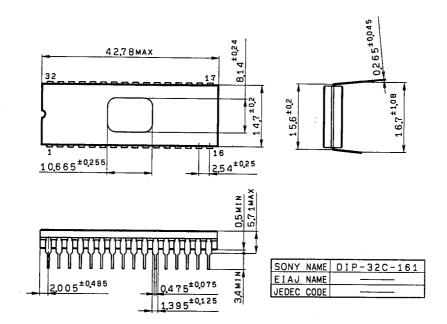

Package Outline

Unit: mm

32 pin DIP (Ceramic)