# M5M5117FP, -15

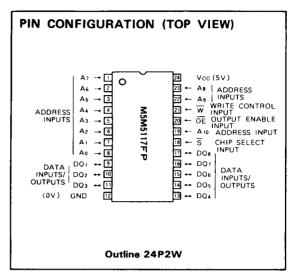

## 16384-BIT (2048-WORD BY 8-BIT) CMOS STATIC RAM

#### DESCRIPTION

The M5M5117FP series of 2048-word by 8-bit asynchronous silicon gate CMOS static RAM operates on a single 5V power supply and is designed for easy use in applications requiring battery backup.

A chip select input,  $\overline{S}$ , is available to provide the minimum standby current with battery back-up while an output enable input,  $\overline{OE}$ , enables high-speed memory access.

The series features pin compatibility with the M5L2716K 16K EPROM and M58725P 16K static RAM, and it is packaged in a small 24-pin plastic DIL flat package.

#### **FEATURES**

| Type name    | A +:                 | OE access     | Current consumption |                   |  |  |

|--------------|----------------------|---------------|---------------------|-------------------|--|--|

|              | Access time<br>(max) | time<br>(max) | Active<br>(max)     | Stand-by<br>(max) |  |  |

| M5M5117FP-15 | 150ns                | <b>80</b> ns  | FO 4                | 15 <i>µ</i> A     |  |  |

| M5M5117FP    | 200ns                | 100ns         | 50mA                | 15,444            |  |  |

- Single 5V power supply.

- External clock and refresh operation not required.

- Data can be held with 2V supply voltage.

- All inputs, and outputs are directly TTL compatible.

- All outputs are 3-state with OR-tie capability.

- Easy expansion of memory capacity with chip select signal.

- Common input/output for data pins.

- Pin compatibility with M5L2716K 16K EPROM and M58725P 16K static RAM.

## **APPLICATIONS**

Battery drive, small-capacity memory units with battery back-up

### **FUNCTION**

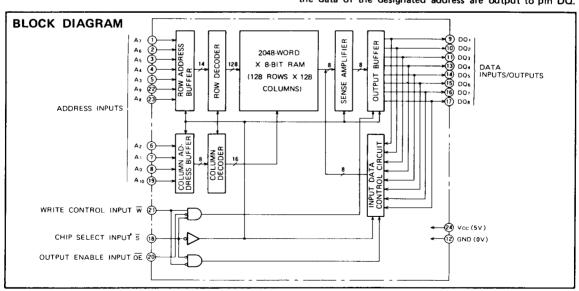

The M5M5117FP series has a 2048-word by 8-bit configuration. It operates on a single 5V supply and its inputs/ outputs are directly TTL compatible. Its completely static circuitry obviates the need for external clock and refresh operations and makes it very easy to use.

The data of the DQ pin are written when the address is designated by address signals  $A_0 \sim A_{10}$ , the  $\overline{S}$  signals turns low-level, and the  $\overline{W}$  signal is set low.

When for the reading operation the  $\overline{W}$  signal is set high, the  $\overline{S}$  and  $\overline{OE}$  signals are set low, pin DQ is set to the output mode and the address is designated by signals  $A_0 \sim A_{10}$ , the data of the designated address are output to pin DQ.

When signal  $\overline{S}$  is set high, the chip is set to a non-select status in which neither reading nor writing is possible. Since the output floats (high-impedance state), OR-tie is possible with the other chip output pins. When the  $\overline{OE}$  signal is set high, the output is put in the floating state. When  $\overline{OE}$  is set high during writing for use with an I/O bus system, bus contention between the input and output data can be avoided.

The standby mode is established when signal  $\overline{S}$  is set to  $V_{CC}$ . The supply current is now reduced to the very low level of 15 $\mu$ A (max) and the data in the memory are

retained even if the supply voltage falls to 2V, permitting power-down during non-operation or battery back-up during power failures.

### **OPERATION MODES**

| S | ŌĒ | $\overline{w}$ | Mode           | DQ             | Icc     |

|---|----|----------------|----------------|----------------|---------|

| Н | х  | Х              | Non-select     | High impedance | Standby |

| L | х  | L              | Write          | DiN            | Active  |

| L | L  | Ι              | Read           | Dout           | Active  |

| L | н  | н              | Output disable | High impedance | Active  |

#### ABSOLUTE MAXIMUM RATINGS

| Symbol          | Parameter                              | Conditions          | Limits                    | Unit |

|-----------------|----------------------------------------|---------------------|---------------------------|------|

| V <sub>CC</sub> | Supply voltage                         |                     | -0.3-7                    | ٧    |

| Vi              | Input voltage                          | With respect to GND | -0.3~V <sub>CC</sub> +0.3 | ٧    |

| Vo              | Output voltage                         |                     | 0~V <sub>CC</sub>         | ٧    |

| Pd              | Power dissipation                      | Ta = 25°C           | 700                       | mW   |

| Торг            | Operating free-air ambient temperature |                     | 0~70                      | °C   |

| Tstg            | Storage temperature                    |                     | <b>−65 ~150</b>           | °c   |

## RECOMMENDED OPERATING CONDITIONS ( $T_a = 0 \sim 70^{\circ}C$ , unless otherwise noted)

|        | Parameter                |      | Unit |                      |      |

|--------|--------------------------|------|------|----------------------|------|

| Symbol | Parameter                | Min  | Тур  | Max                  | Unit |

| Vcc    | Supply voltage           | 4.5  | 5    | 5.5                  | ٧    |

| GND    | Supply voltage           |      | 0    |                      | ٧    |

| VIL    | Low-level input voltage  | -0.3 |      | 0.8                  | ٧    |

| VIH    | High-level input voltage | 2.2  |      | V <sub>CC</sub> +0.3 | ٧    |

### **ELECTRICAL CHARACTERISTICS** ( $T_a = 0 \sim 70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ , unless otherwise noted)

|                | Parameter                                                              |              |                                                              |      | Unit |                      |      |

|----------------|------------------------------------------------------------------------|--------------|--------------------------------------------------------------|------|------|----------------------|------|

| Symbol         |                                                                        |              | Test conditions                                              | Min  | Тур  | Max                  | Unit |

| VIH            | High-level input voltage                                               |              |                                                              | 2.2  |      | V <sub>CC</sub> +0.3 | V    |

| VII.           | Low-level input voltage                                                |              |                                                              | -0.3 |      | 0.8                  | ٧    |

| VoH            | High-level output voltage                                              |              | I <sub>OH</sub> = - 1mA                                      | 2.4  |      |                      | ٧    |

| VoL            | Low-level output voltage                                               |              | I <sub>OL</sub> = 2.1mA                                      |      |      | 0.4                  | ٧    |

| I <sub>I</sub> | Input current                                                          |              | V <sub>1</sub> =0~V <sub>CC</sub>                            |      |      | ± 1                  | μА   |

| lozh           | Off-state high-level output current Off-state low-level output current |              | S or OE = VIH, VO=2.4V-VCC                                   |      |      | 1                    | μΑ   |

| lozu           |                                                                        |              | S or OE = V <sub>IH</sub> , V <sub>O</sub> =0V               |      |      | - 1                  | μA   |

|                |                                                                        | M5M5117FP-15 | V <sub>I</sub> (S) = 0 V Output pin open                     |      |      | 45                   | mA   |

| CC1            | Supply current                                                         | M5M5117FP    | Other inputs = VCC                                           |      | 30   | 45                   | mA   |

|                |                                                                        | M5M5117FP-15 | $V_{I}(\bar{S}) = V_{IL}$ Output pin open                    |      |      | 50                   | mA   |

| I CC2          | Supply current                                                         | M5M5117FP    | Other inputs = V <sub>IH</sub>                               |      | 35   | 50                   | mA   |

| 1 CC3          | Standby supply current                                                 |              | $\overline{S} = V_{CC} - 0.2V$ , Other inputs $= 0 - V_{CC}$ |      |      | 15                   | μA   |

| ICC4           | Standby supply current                                                 |              | $\tilde{S} = V_{IH}$ , Other inputs $= 0 \sim V_{CC}$        |      |      | 2                    | mA   |

| Cı             | Input capacitance (Ta =25°C)                                           |              | V <sub>I</sub> =GND, V <sub>I</sub> =25mVrms, f=1MHz         |      |      | 6                    | pF   |

| Co             | Output capacitance (Ta =                                               | 25°C)        | $V_0 = GND$ , $V_0 = 25mVrms$ , $f = 1MHz$                   |      |      | 8                    | pF   |

Note 1: Current flowing into an IC shall be positive (no sign).

<sup>2:</sup> Typical values: V<sub>CC</sub> = 5V, T<sub>a</sub> = 25°C.

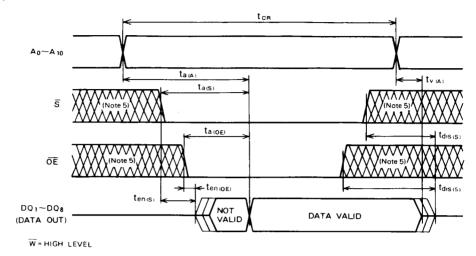

# **SWITCHING CHARACTERISTICS** ( $T_a = 0 \sim 70^{\circ}C$ , $V_{CC} = 5 V \pm 10\%$ , unless otherwise noted) **READ CYCLE**

|                       |                              | M   | M5M5117FP-15<br>Limits |     |     | M5M5117FP<br>Limits |     |    |  |

|-----------------------|------------------------------|-----|------------------------|-----|-----|---------------------|-----|----|--|

| Symbol                | Parameter                    |     |                        |     |     |                     |     |    |  |

|                       |                              | Min | Тур                    | Max | Min | Тур                 | Max |    |  |

| t <sub>CR</sub>       | Read cycle time              | 150 |                        |     | 200 |                     |     | ns |  |

| t <sub>a (A)</sub>    | Address access time          |     |                        | 150 |     |                     | 200 | ns |  |

| ta (S)                | Chip select access time      |     |                        | 150 |     |                     | 200 | ns |  |

| ta (OE)               | Output enable access time    |     |                        | 80  |     |                     | 100 | ns |  |

| tdis(s)               | Output disable time from S   |     | <u>"</u>               | 50  |     |                     | 60  | ns |  |

| t <sub>dis (OE)</sub> | Output disable time from OE  |     |                        | 50  |     |                     | 60  | ns |  |

| t <sub>en (S)</sub>   | Output enable time from S    | 15  |                        |     | 15  |                     |     | ns |  |

| t <sub>en (OE)</sub>  | Output enable time from OE   | 15  |                        |     | 15  |                     |     | ns |  |

| t <sub>v (A)</sub>    | Data valid time from address | 20  |                        |     | 20  |                     |     | ns |  |

# TIMING REQUIREMENTS ( $\tau_a$ = 0 $\sim$ 70°C , $~V_{CC}$ = 5 V $\pm$ 10% , unless otherwise noted ) WRITE CYCLE

|                      |                                | М   | M5M5117FP-15<br>Limits |     |     | M5M5117FP<br>Limits |     |          |

|----------------------|--------------------------------|-----|------------------------|-----|-----|---------------------|-----|----------|

| Symbol               | Parameter                      |     |                        |     |     |                     |     |          |

|                      |                                | Min | Тур                    | Max | Min | Тур                 | Max | <u> </u> |

| t <sub>CW</sub>      | Write cycle time               | 150 |                        |     | 200 |                     |     | ns       |

| t <sub>w(w)</sub>    | Write pulse width              | 90  |                        |     | 120 |                     |     | ns       |

| t <sub>su (A)</sub>  | Address set-up time            | 0   |                        |     | 0   |                     |     | ns       |

| t <sub>su(s)</sub>   | Chip select set-up time        | 90  |                        |     | 120 |                     |     | ns       |

| t <sub>su(D)</sub>   | Data set-up time               | 40  | *                      |     | 60  |                     |     | ns       |

| t <sub>h (D)</sub>   | Data hold time                 | 0   |                        |     | 0   |                     |     | ns       |

| trec(w)              | Write recovery time            | 10  |                        |     | 10  |                     |     | ns       |

| t <sub>su(OE)</sub>  | Output enable set-up time      | 40  |                        |     | 40  |                     |     | ns       |

| t <sub>dis(OE)</sub> | Output disable time from OE    |     |                        | 50  |     |                     | 60  | ns       |

| t <sub>dis (w)</sub> | Output disable time from write | -   |                        | 50  |     |                     | 60  | ns       |

| ten (w)              | Output enable time from write  | 15  |                        |     | 15  |                     |     | ns       |

##

| Combal               |                           | Test conditions                       | Limits |          |     |      |

|----------------------|---------------------------|---------------------------------------|--------|----------|-----|------|

| Symbol               | Parameter                 | rest conditions                       | Min    | Тур      | Max | Unit |

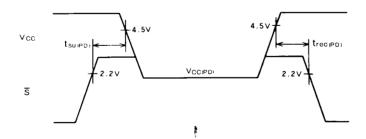

| V <sub>CC</sub> (PD) | Power-down supply voltage |                                       | 2      |          |     | ٧    |

| .,                   | Chip select input voltage | 2.2V≦V <sub>CC</sub> (PD)             | 2.2    |          |     | ٧    |

| V <sub>I</sub> (S)   |                           | 2V ≤ V <sub>CC</sub> (PD) ≤ 2.2 V     |        | VCC (PD) |     | . v  |

| CC (PD)              | Power-down supply current | V <sub>CC</sub> =3V, Other inputs =3V |        |          | 10  | μА   |

Note 3: When  $\overline{S}$  is operated at 2.2V (V<sub>IH</sub> min), the supply current at which V<sub>CC (PD)</sub> is between 4.5V and 2.4V, is specified by I<sub>CC4</sub>.

#### TIMING REQUIREMENTS (Ta=0~70°C, unless otherwise noted)

| Symbol Parameter      | Parameter                | Test conditions | Limits          |     |     | Unit |

|-----------------------|--------------------------|-----------------|-----------------|-----|-----|------|

| Symbol                | - Additional             | rest conditions | Min             | Тур | Max | Onit |

| t <sub>su (PD)</sub>  | Power-down set-up time   |                 | 0               |     |     | ns   |

| t <sub>rec (PD)</sub> | Power-down recovery time |                 | t <sub>CR</sub> |     |     | ns   |

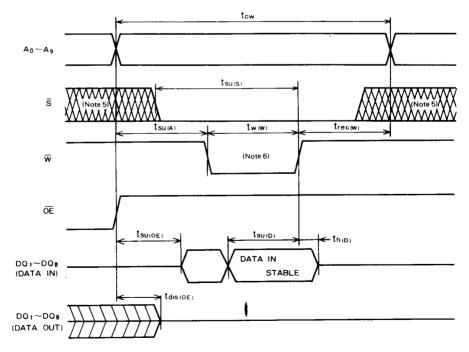

# TIMING DIAGRAM Read cycle

## Write cycle (W control)

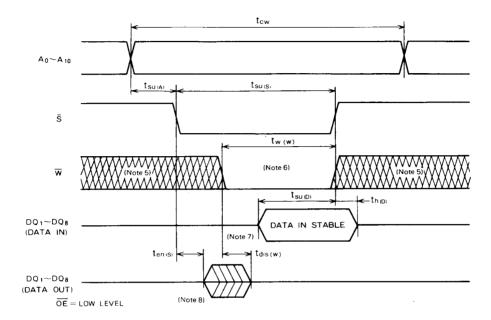

## Write cycle (\$\overline{S}\$ control)

Note 4 Test conditions Input pulse level:  $0.4 \simeq 2.4 \text{V}$  Input pulse risetime and falltime: 10ns Load: 1TTL,  $C_L = 100 \text{pF}$  Reference level: 1.5 V

- Note 5: Hatching indicates the don't care inputs.

- Writing is performed while S and W are in the low-level overlap period.

- 7: The output is kept in the high-impedance state when  $\overline{W}$  falls simultaneously with, or before, the  $\overline{S}$  falls.

- 8: A reverse phase signal should not be supplied when DQ is in the output mode.

### **POWER-DOWN CHARACTERISTICS**