# Description

The µPD27C512 is an ultraviolet erasable, electrically programmable 524,288-bit ROM fabricated with an advanced CMOS process for substantial power savings. The device is organized as 64K words by 8 bits and operates from a single +5-volt power supply. All inputs and outputs are TTL-compatible. The device is available in a 28-pin cerdip package with quartz window.

#### **Features**

- ☐ 64K x 8-bit organization

- ☐ Ultraviolet erasable and electrically programmable

- ☐ High-speed programming mode

- □ Low power dissipation

- 30 mA max (active)

- 100 μA max (standby)

- ☐ TTL-compatible inputs and outputs

- ☐ Single +5-volt power supply

- ☐ Three-state outputs

- ☐ Advanced CMOS technology

- ☐ 28-p n cerdip with quartz window

# **Ordering Information**

| Part Number   | Access Time (max) | Package            |

|---------------|-------------------|--------------------|

| μPD27C512D-15 | 150 ns            | 28-pin cerdip with |

| D-20          | 200 ns            | quartz window      |

#### Pin Identification

| Symbol                          | Function                      |

|---------------------------------|-------------------------------|

| A <sub>0</sub> -A <sub>15</sub> | Address inputs                |

| 0 <sub>0</sub> -0 <sub>7</sub>  | Data outputs                  |

| <u>CE</u>                       | Chip enable                   |

| OE/V <sub>PP</sub>              | Output enable/program voltage |

| GND                             | Ground                        |

| v <sub>cc</sub>                 | Power supply                  |

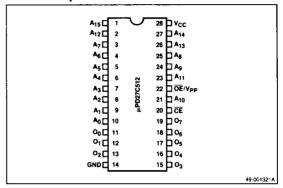

# **Pin Configuration**

#### 28-Pin Cerdip

# **Absolute Maximum Ratings**

| Output voltage, V <sub>0</sub>          | −0.6 to +7.0 V  |

|-----------------------------------------|-----------------|

| Input voltage, V <sub>1</sub>           | −0.6 to +7.0 V  |

| Input voltage, A <sub>9</sub>           | -0.6 to +13.5 V |

| Supply voltage, V <sub>CC</sub>         | -0.6 to +7.0 V  |

| Supply voltage, V <sub>PP</sub>         | -0.6 to +13.5 V |

| Operating temperature, T <sub>OPR</sub> | -10 to +80°C    |

| Storage temperature, T <sub>STG</sub>   | −65 to +125°C   |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

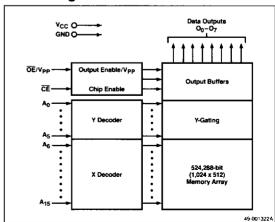

# **Block Diagram**

| Mo | de | Sel | lec | tic | 'n |

|----|----|-----|-----|-----|----|

|    |    |     |     |     |    |

| Mode            | CE              | OE/V <sub>PP</sub> | V <sub>CC</sub> | Outputs          |

|-----------------|-----------------|--------------------|-----------------|------------------|

| Read            | V <sub>JL</sub> | V <sub>IL</sub>    | +5 V            | D <sub>OUT</sub> |

| Output disable  | VIL             | V <sub>tH</sub>    | +5 V            | High-Z           |

| Staniby         | V <sub>IH</sub> | Х                  | +5 V            | High-Z           |

| Program         | ν <sub>IL</sub> | Vpp                | +6 V            | DiN              |

| Program verify  | V <sub>IL</sub> | V <sub>IL</sub>    | +6 V            | D <sub>OUT</sub> |

| Program inhibit | V <sub>iH</sub> | Vpp                | +6 V            | High-Z           |

# Capacitance T<sub>A</sub> = 25 °C; f = 1 MHz

|                    |                  |     | Limits |     |      |                                      |  |

|--------------------|------------------|-----|--------|-----|------|--------------------------------------|--|

| Parameter          | Symbol           | Min | Тур    | Max | Unit | Test Conditions                      |  |

| Input              | C <sub>IN1</sub> |     |        | 6   | pF   | V <sub>I</sub> = 0 V                 |  |

| capacitance        | C <sub>IN2</sub> |     |        | 20  | pF   | $\overline{0E}/V_{PP}$ ; $V_j = 0 V$ |  |

| Output capacitance | C <sub>OUT</sub> |     |        | 12  | pF   | $V_0 = 0 V$                          |  |

#### Notes:

(1)  $X = V_{IL} \text{ or } V_{IH}$

DC Characteristics

T<sub>A</sub> = 0 to +70 °C; V<sub>CC</sub> = 5.0 V ±10%

|                                                                  | Limits                         |                       |     |                       |      |                                                         |

|------------------------------------------------------------------|--------------------------------|-----------------------|-----|-----------------------|------|---------------------------------------------------------|

| Parameter                                                        | Symbol                         | Min                   | Тур | Max                   | Unit | Test Conditions                                         |

| Read and Standby Mo                                              | des                            |                       |     |                       |      |                                                         |

| Input voltage, high                                              | V <sub>IH</sub>                | 2.0                   |     | V <sub>CC</sub> + 0.3 | γ    |                                                         |

| Input voltage, low                                               | V <sub>IL</sub>                | -0.3                  |     | 8.0                   | ٧    |                                                         |

| Outout voltage, high                                             | V <sub>OH1</sub>               | 2.4                   |     |                       | V    | $I_{OH} = -400  \mu A$                                  |

|                                                                  | V <sub>0H2</sub>               | V <sub>CC</sub> - 0.7 |     |                       | ٧    | $I_{OH} = -100 \mu\text{A}$                             |

| Output voltage, low                                              | V <sub>OL</sub>                |                       |     | 0.45                  | ٧    | $I_{OL} = 2.1 \text{ mA}$                               |

| Output leakage current                                           | lro                            |                       |     | 10                    | μΑ   | $V_0 = 0$ to $V_{CC}$ ; $\overline{OE} = V_{1H}$        |

| Input leakage current                                            | Լլյ                            |                       |     | 10                    | μA   | $V_i = 0$ to $V_{CC}$                                   |

| V <sub>C()</sub> current, active                                 | ICCA1                          |                       |     | 30                    | mA   | $\overline{CE} = V_{IL}; V_I = V_{IH}$                  |

|                                                                  | ICCA2                          |                       |     | 30                    | mA   | $f \approx 5 \text{ MHz}$ ; $I_{OUT} = 0 \text{ mA}$    |

| V <sub>CC</sub> current, standby                                 | I <sub>CCS1</sub>              |                       |     | 1                     | mA   | $\overline{\text{CE}} = V_{1H}$                         |

|                                                                  | Iccs2                          |                       | 1   | 100                   | μΑ   | $\overline{CE} = V_{CC}$ ; $V_I = 0$ to $V_{CC}$        |

| Programming Modes<br>$T_A = 25 \pm 5$ °C; $V_{CC} = 6.0 \pm 6.0$ | 0.25 V; V <sub>PP</sub> = 12.5 | ±0.3 V                |     |                       |      |                                                         |

| Input voltage, high                                              | V <sub>IH</sub>                | 2.0                   |     | $V_{CC} + 0.3$        | ٧    | •                                                       |

| Input voltage, low                                               | V <sub>IL</sub>                | -0.3                  |     | 0.8                   | ٧    |                                                         |

| Input leakage current                                            | lLi                            |                       |     | 10                    | μА   | NI = NIT or NIH                                         |

| Output voltage, high                                             | V <sub>OH</sub>                | 2.4                   |     |                       | ٧    | $I_{OH} = -400 \mu\text{A}$                             |

| Output voltage, low                                              | V <sub>OL</sub>                |                       |     | 0.45                  | ٧    | I <sub>OL</sub> = 2.1 mA                                |

| V <sub>PP</sub> current                                          | lpp                            |                       |     | 30                    | mA   | $\overline{CE} = V_{IL}; \overline{OE}/V_{PP} = V_{IH}$ |

| V <sub>CC</sub> current                                          | Icc                            |                       |     | 30                    | mA   |                                                         |

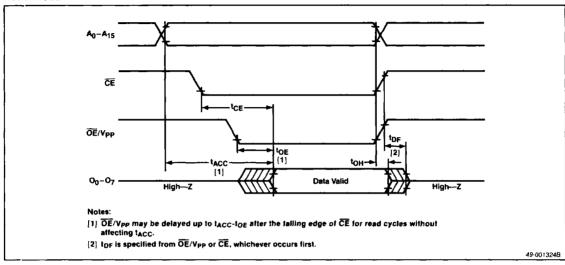

# **AC Characteristics, Read and Standby Modes**

$T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%$

|                                                                       |                 |                       | Lir | nits         |     |      |                                                       |

|-----------------------------------------------------------------------|-----------------|-----------------------|-----|--------------|-----|------|-------------------------------------------------------|

| Parameter                                                             | Symbol          | μ <b>P</b> 027C512-15 |     | μPD27C512-20 |     |      |                                                       |

|                                                                       |                 | Min                   | Max | Min          | Max | Unit | Test Conditions                                       |

| Address to output delay                                               | tacc            |                       | 150 |              | 200 | ns   | $\overline{CE} = \overline{OE}/V_{PP} \approx V_{IL}$ |

| CE to output delay                                                    | t <sub>CE</sub> |                       | 150 |              | 200 | ns   | $\overline{OE}/V_{PP} = V_{JL}$                       |

| OE/V <sub>PP</sub> to output delay                                    | t <sub>OE</sub> |                       | 75  |              | 75  | ns   | CE = V <sub>IL</sub>                                  |

| OE/V <sub>PP</sub> high to output float                               | tDF             | 0                     | 60  | 0            | 60  | ns   | $\overline{CE} = V_{1L}$                              |

| Output hold from address, CE or OE, whichever transition occurs first | tон             | 0                     |     | 0            |     | ns   | $\overline{CE} = \overline{OE}/V_{PP} = V_{IL}$       |

#### Notes:

(1) Output load: see figure 1. Input rise and fall times ≤ 20 ns. Input pulse levels: 0.45 and 2.4 V. Timing measurement reference levels: inputs and outputs = 0.8 and 2.0 V

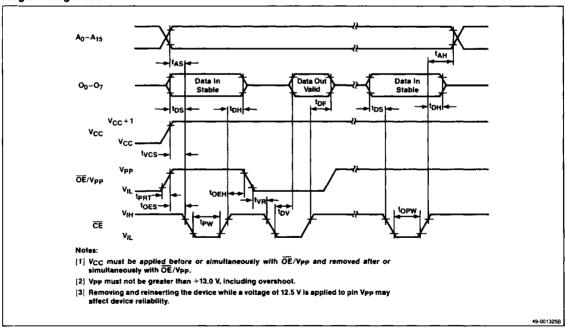

# AC Characteristics, Programming Modes $T_A=25\pm5\,^{\circ}\text{C};\,V_{CC}=6.0\pm0.25\,\text{V};\,V_{PP}=12.5\pm0.3\,\text{V}$

| Parameter                        | •                |      | Limits |       |      |                                 |

|----------------------------------|------------------|------|--------|-------|------|---------------------------------|

|                                  | Symbol           | Min  | Тур    | Max   | Unit | <b>Test Conditions</b>          |

| Address setup time               | tas              | 2    |        |       | μS   |                                 |

| DE setup time                    | t <sub>OES</sub> | 2    |        |       | μS   |                                 |

| Data setup time                  | t <sub>DS</sub>  | 2    | -      |       | μS   |                                 |

| Address hold time                | t <sub>AH</sub>  | 2    |        |       | μS   |                                 |

| Data hold time                   | t <sub>DH</sub>  | 2    |        |       | μS   |                                 |

| CE to output float time          | t <sub>DF</sub>  | 0    |        | 130   | ns   |                                 |

| V <sub>CC</sub> set up time      | tycs             | 2    |        |       | μS   |                                 |

| Initial program pulse width      | tpw              | 0.95 | 1.0    | 1.05  | ms   |                                 |

| Overprogram pulse width          | topw             | 2.85 |        | 78.75 | ms   |                                 |

| CE to output delay               | t <sub>DV</sub>  |      |        | 1     | μS   | $\overline{0E}/V_{PP} = V_{IL}$ |

| OE/V <sub>PP</sub> hold time     | t <sub>DEH</sub> | 2    |        |       | μS   |                                 |

| OE/V <sub>PP</sub> recovery time | t <sub>VR</sub>  | 2    |        |       | μS   |                                 |

| OE/V <sub>PP</sub> rise time     | tPRT             | 50   |        |       | ns   |                                 |

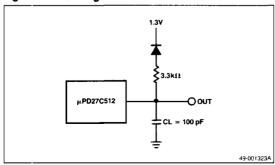

Figure 1. Loading Conditions Test Circuit

# **Timing Waveforms**

#### Read Mode

#### Programming Mode

# **Programming Operation**

### **High-Speed Programming Mode**

Begin programming by erasing all data; this places all bits in the high-level (1) state. Enter data by programming a low-level (0) TTL signal into the chosen bit location.

Address the first location and apply valid data at the eight output pins. Raise  $V_{CC}$  to +6 V  $\pm 0.25$  V; then raise  $\overline{CE}/V_{PP}$  to +12.5 V  $\pm 0.3$  V. Apply a 1-ms ( $\pm 5\%$ ) program pulse to  $\overline{CE}$  as shown in the programming mode timing waveform. The bit is verified and the program/no-program decision is made. If the bit is not programmed, apply another 1-ms pulse to  $\overline{CE}$ , up to a maximum of 25 times. If the bit is programmed within 25 tries, apply an additional overprogram pulse of "x" ms (where "x" equals the number of tries multiplied by 3) and input the next address. If the bit is not programmed in 25 tries, reject the device as a program failure.

### **Programming Inhibit Mode**

Use the programming inhibit mode to program multiple  $\mu$ PD27C512s connected in parallel. All like inputs (except  $\overline{CE}$ , but including  $\overline{OE}/V_{PP}$ ) may be common. Program individual devices by applying a low-level (0) TTL bulse to the  $\overline{CE}$  input of the  $\mu$ PD27C512 to be programmed. Applying a high level (1) to the  $\overline{CE}$  input of the other devices prevents them from being programmed.

#### **Program Verify Mode**

Perform verification on the programmed bits to determine that the data was correctly programmed. The program verification can be performed with  $\overline{CE}$  and  $\overline{OE}/V_{PP}$  at low levels (0).

#### **Erasure**

Erase data on the  $\mu$ PD27C512 by exposing it to light with a wavelength shorter than 400 nm. Exposure to direct sunlight or fluorescent light could also erase the data. Consequently, mask the window to prevent unintentional erasure by ultraviolet rays.

Data is typically erased by 254-nm ultraviolet rays. A minimum lighting level of 15 W sec/cm<sup>2</sup> (ultraviolet ray intensity multiplied by exposure time) is required to completely erase written data.

An ultraviolet lamp rated at  $12,000 \mu \text{W/cm}^2$  takes approximately 15 to 20 minutes to complete erasure. Place the  $\mu \text{PD27C512}$  within 2.5 cm of the lamp tubes. Remove any filter on the lamp.