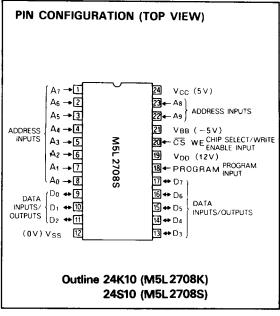

# 8192-BIT (1024-WORD BY 8-BIT) ERASABLE AND ELECTRICALLY REPROGRAMMABLE ROM

#### **DESCRIPTION**

This is a family of FAMOS (floating-gate avalanche-injection MOS) ultraviolet-light erasable and electrically reprogrammable 8192-bit (1024-word by 8-bit) EPROMs. They incorporate N-channel silicon-gate MOS technology, are designed for microcomputer system applications, and have direct TTL-compatibility for all inputs and outputs, without extra interface circuits.

#### **FEATURES**

Fast programming: 100s/8192 bits (typ)

Access time:

M5L 2708K, S: 450ns (max) M5L 270K-65, S-65: 650ns (max)

- Low power dissipation during programming

- No clocks required; the circuitry is entirely static

- Data inputs and outputs TTL-compatible during read and program modes

- Easy memory expansion by chip-select/write-enable (CS/WE) input

- Typical power supply voltages: 12V, 5V, -5V

- For large volume production; pin compatible with the Mitsubishi M58730-XXXS mask-programmable ROM

- Interchangeable with Intel's 2708 in pin configuration and electrical characteristics

#### **APPLICATION**

Computers and peripheral equipment

#### **FUNCTION**

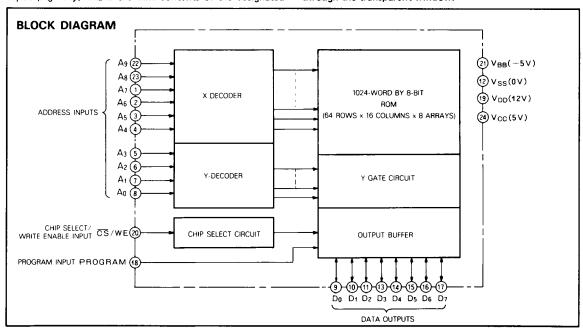

Read—Set the  $\overline{CS}/WE$  terminal to the read mode (0~5V). Low-level input to  $\overline{CS}/WE$  and address signals to the address input (A<sub>0</sub> ~A<sub>9</sub>) make the data contents of the designated

address location available at the data inputs/outputs  $(D_0 \sim D_7)$ . When the  $\overline{CS}/WE$  signal is high, data inputs/outputs  $(D_0 \sim D_7)$  are in a floating state.

Write—Set the  $\overline{CS}/WE$  terminal to the write mode (12V). A program pulse will effect the write operation for the data at each address loaded via data inputs/outputs  $(D_0 \sim D_7)$ . For details refer to the description of the programming mode,

Erase—Erase is effected by exposure to ultraviolet light through the transparent window.

# 8192-BIT (1024-WORD BY 8-BIT) ERASABLE AND ELECTRICALLY REPROGRAMMABLE ROM

## **FUNCTIONAL OPERATIONS**

#### **Programming Procedure**

These devices are in the '1' state (with high-level output) after erase, and go into the '0' state (with low-level output) after programming. All bits of the M5L 2708S, S-65 are initially in the '1' state, and must be programmed according to the following procedures.

The chip enters the program mode when 12V is supplied to the  $\overline{\text{CS}}/\text{WE}$  input (pin 20). Data to be programmed are presented, 8 bits in parallel, to the data inputs/outputs  $(D_0 \sim D_7)$  and the addresses are set up by the address inputs. After address and data set-up, one program pulse is applied to the program input (pin 18) for each address from 0 to 1023. This pass through all addresses, known as a program loop, must be repeated a number of times, N, which depends upon the width of the program pulse and must satisfy the condition  $N \cdot t_{W\{p\}} \ge 100 \text{ms}$ .

#### **Erase Procedure**

These devices can be erased by exposure to high-intensity short-wave ultraviolet light at a wavelength of 2537Å through the transparent lid provided. The required exposure is approximately  $15 \text{Ws/cm}^2$ . If the energy of the lamp used is unknown, find the total time ( $t_E$ ) required to erase all bits and use a short-wave ultraviolet-light exposure time of 3 to 5 times this value.

### HANDLING PRECAUTIONS FOR FAMOS DEVICES

In addition to general handling precautions for MOS devices, the following points apply to FAMOS devices.

- High voltages are used when programming, and the conditions under which it is performed must be carefully controlled to prevent the application of excessively high voltages

- Before erasing, clean the surface of the transparent lid to remove completely oily impurities, which may impede irradiation and affect the erasing characteristics.

- 3 This ultraviolet-light erasable PROM is erasable by ultraviolet-light with wavelengths under 4000Å. For use involving long exposure to direct sunlight or to lamps radiating at these wavelengths, the transparent window should be covered with opaque tape.

# 8192-BIT (1024-WORD BY 8-BIT) ERASABLE AND ELECTRICALLY REPROGRAMMABLE ROM

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                                                                  | Conditions                      | Limits   | Unit  |

|-----------------|----------------------------------------------------------------------------|---------------------------------|----------|-------|

| V11             | Input voltage, V <sub>DD</sub> and CS/WE write mode                        |                                 | -0.3-20  | V     |

| V <sub>12</sub> | Input voltage, V <sub>CC</sub> , V <sub>SS</sub> , address and data signal | With respect to V <sub>BB</sub> | -0.3-15  | V     |

| V <sub>13</sub> | Input voltage, program mode                                                | 1                               | -0.3~35  | V     |

| Торг            | Operating free-air temperature range                                       |                                 | 0 ~ 70   | ٣     |

| Tstg            | Storage temperature range                                                  |                                 | -65 -125 | TC TC |

#### **READ OPERATION**

### Recommended Operating Conditions (Ta = 0 ~70 ℃, unless otherwise noted)

| Symbol          | Parameter                |       | Limits |                    | 1 lais |  |

|-----------------|--------------------------|-------|--------|--------------------|--------|--|

| Symbol          | Farameter                | Min   | Nom    | Max                | Unit   |  |

| Vcc             | Supply voltage           | 4.75  | 5      | 5, 25              | ٧      |  |

| V <sub>DD</sub> | Supply voltage           | 11.4  | 12     | 12.6               | V      |  |

| VBB             | Supply voltage           | -4.75 | -5     | -5.25              | ٧      |  |

| Vss             | Supply voltage (GND)     |       | 0      |                    | ٧      |  |

| VIL             | Low-level input voltage  | Vss   |        | 0.65               | V      |  |

| VIH             | High-level input voltage | 3     |        | V <sub>CC</sub> +1 | V      |  |

#### **Electrical Characteristics**

$T_a = 0 \sim 70 \, \text{C}, \quad V_{CC} = 5 \, \text{V} \pm 5\%, \quad V_{DD} = 12 \, \text{V} \pm 5\%, \quad V_{BB} = -5 \, \text{V} \pm 5\%, \quad V_{SS} = 0 \, \text{V}. \quad \text{unless otherwise noted. Note 1}$

| Symbol           | Parameter                                           | Test conditions                                  |     | Limits |      | Unit |

|------------------|-----------------------------------------------------|--------------------------------------------------|-----|--------|------|------|

| Symbol           | raianietei                                          | rest conditions                                  | Min | Тур    | Max  | Orac |

| I <sub>IL</sub>  | Low-level input current, address, chip select input | V <sub>1</sub> =5.25V                            |     |        | 10   | μΑ   |

| loz              | Off-state (high-impedance-state) output current     | $V_0 = 5.25V$ , $V_0(\overline{CS} WE) = 5V$     |     |        | 10   | μΑ   |

| IDD              | Supply current from V <sub>DD</sub>                 | Worst case.                                      |     | 50     | 65   | mΑ   |

| lcc              | Supply current from VCC                             | all inputs high.                                 |     | 6      | 10   | mA   |

| IBB              | Supply current from VBB                             | V <sub>O</sub> ( <del>CS</del> we) =5 V, Ta =0 ℃ |     | 30     | 45   | mA   |

| VoL              | Low-level output voltage                            | IOL=1.6mA                                        |     |        | 0.45 | ٧    |

| V <sub>OH1</sub> | High-level output voltage                           | I <sub>OH</sub> = -100 $\mu$ A                   | 3.7 |        | 1    | ٧    |

| V <sub>OH2</sub> | High-level output voltage                           | I <sub>OH</sub> = -1 mA                          | 2.4 |        |      | V    |

| Pd               | Power dissipation                                   | Ta = 70 ℃                                        |     |        | 800  | mW   |

| Ci               | Input capacitance                                   | )/ 0\/ f 1\                                      |     | 4      | 6    | pF   |

| Co               | Output capacitance                                  | V <sub>1</sub> =0V, f=1MHz                       |     | 8      | 12   | pF   |

Note 1: Typical values are at Ta = 25 °C and nominal supply voltage

## $\textbf{Switching Characteristics} \ \ (T_a = 0 \sim 70 \, \text{T}, \ \ V_{CC} = 5 \, \text{V} \pm 5 \, \text{\%}, \ \ V_{DD} = 12 \, \text{V} \pm 5 \, \text{\%}, \ \ V_{BB} = -5 \, \text{V} \pm 5 \, \text{\%}, \ \ V_{SS} = 0 \, \text{V} \, . \ \ \text{unless otherwise noted)}$

| Symbol    | Parameter                              | Test conditions            | Limits |         |     |      |    |

|-----------|----------------------------------------|----------------------------|--------|---------|-----|------|----|

|           |                                        | rest conditions            | Min    | Min Typ | Max | Unit |    |

|           |                                        | M5L 2708K, S               |        |         | 280 | 450  | ns |

| ta(AD)    | Address access time M5L 2708K-65, S-65 |                            |        |         | 650 | ns   |    |

| ta(CS)    | Chip select access time                |                            |        |         | 60  | 120  | ns |

| tdv(CSLH) | Data valid time with respect           | to chip select low-to-high |        | 0       |     | 120  | ns |

| tdv(AD)   | Data valid time with respect           | to address                 |        | 0       |     |      | ns |

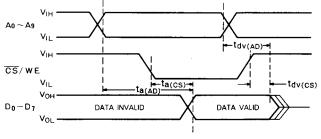

#### **Timing Diagram**

#### **Test Conditions for Switching Characteristics**

$\begin{array}{ll} \mbox{Input voltage:} & V_{1L}\!=\!0.65\mbox{V}, & V_{1H}\!=\!3\mbox{V} \\ \mbox{Reference voltage at timing measurement:} & \mbox{Input} & 0.8\!\sim\!2.8\mbox{V} \\ & \mbox{output} & 0.8\!\sim\!2.4\mbox{V} \end{array}$

# 8192-BIT (1024-WORD BY 8-BIT) ERASABLE AND ELECTRICALLY REPROGRAMMABLE ROM

#### PROGRAM OPERATION

Recommended Operating Conditions ( $T_a=25$ °C,  $V_{CC}=5$ V $\pm5$ %,  $V_{DD}=12$ V $\pm5$ %,  $V_{BB}=-5$ V $\pm5$ %,  $V_{SS}=0$ V, unless otherwise noted)

| Symbol              | Parameter                                     |                 | Limits |       | Unit |

|---------------------|-----------------------------------------------|-----------------|--------|-------|------|

|                     | - Columbia                                    | Min             | Nom    | Max   | Onit |

| VIL1(P)             | Low-level input voltage, except program input | Vss             |        | 0.65  | V    |

| VIH1(P)             | High-level input voltage, address, data input | 3               |        | Vcc+1 |      |

| V <sub>IH2(P)</sub> | High-level input voltage, CS/WE               | 11.4            |        | 12.6  | V    |

| V <sub>IH3(P)</sub> | High-level input voltage, program mode 2      | 25              |        | 27    | V    |

| VIL2(P)             | Low-level input voltage, program mode 3       | V <sub>SS</sub> |        | 1     | V    |

Note 2 : With respect to V<sub>SS</sub>

3: Where  $V_{1H3(P)} - V_{1L2(P)} = 25V(min)$

$\textbf{Electrical Characteristics} \ ( \ \ \, \text{$V_{\text{CC}}$=5$V$} \pm 5\%, \ \ V_{\text{DD}} = 12$V$ \pm 5\%, \ \ V_{\text{BB}} = -5$V$ \pm 5\%, \ \ V_{\text{SS}} = 0$V$, unless otherwise noted} )$

| Symbol               | Parameter                                           | Test conditions       |     | Limits |     |      |

|----------------------|-----------------------------------------------------|-----------------------|-----|--------|-----|------|

|                      | T didifficial                                       | Test conditions       | Min | Тур    | Max | Unit |

| IIL1(P)              | Low-level input current, address, chip select input | V <sub>I</sub> =5.25V |     |        | 10  | μА   |

| I <sub>IL2</sub> (P) | Low-level input current, program input              |                       |     |        | 3   | mA   |

| IH1(P)               | High-level current, program input                   |                       |     |        | 20  | mA   |

| IDD                  | V <sub>DD</sub> supply current                      | Worst case,           |     | 50     | 65  | mA   |

| Icc                  | V <sub>CC</sub> supply current                      | all inputs high4      |     | 6      | 10  | mA   |

| I <sub>BB</sub>      | V <sub>BB</sub> supply current                      | CS/WE =5 V. Ta =0 ℃   |     | 30     | 45  | mΑ   |

Note 4: Typical values are at Ta=25℃ and nominal supply voltage.

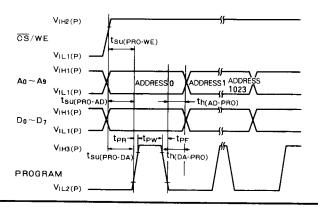

## Timing Requirements ( $T_a = 25 \text{ C}$ , $V_{CC} = 5 \text{ V} \pm 5 \text{ W}$ , $V_{DD} = 12 \text{ V} \pm 5 \text{ W}$ , $V_{BB} = -5 \text{ V} \pm 5 \text{ W}$ , $V_{SS} = 0 \text{ V}$ , unless otherwise noted)

| Symbol                  | Parameter                                         | Test conditions | Limits |     |     |      |

|-------------------------|---------------------------------------------------|-----------------|--------|-----|-----|------|

|                         | T didnister                                       | Test Conditions | Min    | Тур | Max | Unit |

| t <sub>SU(PRO-AD)</sub> | Program setup time with respect to address        |                 | 10     |     |     | μS   |

| t <sub>SU(PRO-WE)</sub> | Program setup time with respect to WE low-to-high |                 | 10     |     |     | μs   |

| tsu(PRO-DA)             | Program setup time with respect to data           |                 | 10     |     |     | μS   |

| th(AD-PRO)              | Address hold time with respect to program         |                 | 1      |     |     | μS   |

| th(WE-PRO)              | WE hold time with respect to program              |                 | 0.5    |     |     | μS   |

| th(DA-PRO)              | Data hold time with respect to program            |                 | 1      |     |     | μS   |

| tw(P)                   | Program pulse width                               |                 | 0.1    |     | 1   | ms   |

| tr(P)                   | Program rise time                                 |                 | 0.5    |     | 2   | μS   |

| tf(P)                   | Program fall time                                 |                 | 0.5    |     | 2   | μs   |

## Switching Characteristics ( $T_a=25\%$ , $V_{CC}=5V\pm5\%$ , $V_{DD}=12V\pm5\%$ , $V_{BB}=-5V\pm5\%$ , $V_{SS}=0V$ , unless otherwise noted)

| Symbol     | Parameter                                      | Test conditions | Limits |     |     | Unit  |

|------------|------------------------------------------------|-----------------|--------|-----|-----|-------|

|            |                                                | Tool Conditions | Min    | Тур | Max | Oriit |

| ta(DA-WE)  | Access time with respect to WE high-to-low     |                 |        |     | 10  | μS    |

| tov(DA-CS) | Data valid time with respect to CS low-to-high |                 | 0      |     | 120 | ns    |

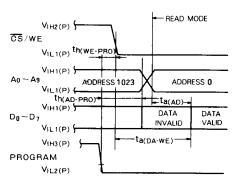

### **Timing Diagram**

### Program Mode

#### From Program Mode to Read Mode