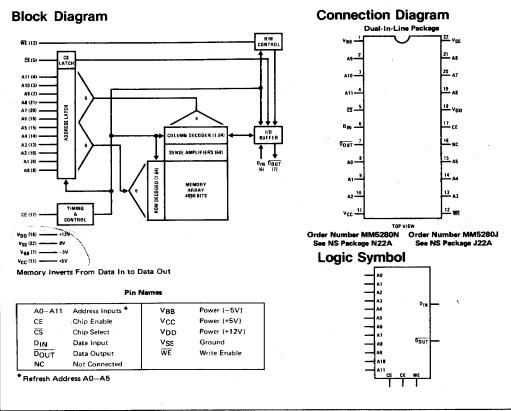

# MM5280 4096-Bit (4096 × 1) Dynamic RAM

#### **General Description**

National's MM5280 is a 4096 word by 1 bit dynamic RAM. It incorporates the latest memory design features and can be used in a wide variety of applications, from those which require very high speed to ones where low cost and large bit capacity are the prime criteria.

The MM5280 must be refreshed every 2 ms. This can be accomplished by performing a read cycle at each of the 64 row addresses (A0-A5). The chip select input can be either high or low for refresh.

The MM5280 has been designed with minimum production costs as a prime criterion. It is fabricated using N-channel silicon gate MOS technology, which is an ideal choice for high density integrated circuits. The MM5280 uses a single transistor cell to minimize the device area. The single device cell, along with unique design features

in the on-chip peripheral circuits, yields a high performance memory device.

#### **Features**

- Organization: 4096 x 1

- Access time 200 ns maximum -

- Cvcle time 400 ns minimum

- Easy system interface

- One high voltage input—chip enable

- TTL compatible—all other inputs and output

- Address registers on-chip

- TRI STATE® output

- Simple read-modify-write operation

- Industry standard pin configuration

### Absolute Maximum Ratings (Note 1)

Storage Temperature -65°C to +150°C

All Input or Output Voltages with Respect

to the Most Negative Supply Voltage, VBB

Supply Voltages VDD, VCC and VSS with -0.3V to +20V

## **Operating Conditions**

MAX UNITS Operating Temperature Range O +70 °c V<sub>DD</sub> Voltage 10.8 13.2 v V<sub>CC</sub> Voltage 4.5 5.5 ٧ V<sub>BB</sub> Voltage -5.5 ٧

#### DC Electrical Characteristics

Respect to VBB

Power Dissipation

$T_A = 0^{\circ}\text{C to } + 70^{\circ}\text{C}, \ V_{DD} = (+12\text{V}) \pm 10\%, \ V_{CC} = +5\text{V}) \pm 10\%, \ V_{BB} \ (\text{Note 2}) = -5\text{V} \pm 10\%, \ V_{SS} = 0\text{V}) \text{ unless otherwise noted}$

- 1.25W

| SYMBOL           | PARAMETER                                             | CONDITIONS                                                                        | MIN                | TYP      | MAX                | UNITS |

|------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------|----------|--------------------|-------|

| I <sub>LI</sub>  | Input Load Current                                    | V <sub>IN</sub> = 0V to V <sub>IH</sub> max, (All Inputs<br>Except CE)            |                    | 0.01     | 10                 | μΑ    |

| ILC              | Input Load Current                                    | V <sub>IN</sub> = DV to V <sub>IHC</sub> max                                      |                    | 0.01     | 10                 | μА    |

| . IILOI          | Output Leakage Current Up For<br>High Impedance State | CE = $V_{ILC}$ or $\overline{CS} = V_{IH}$ , $V_O = 0V$ to 5.25V                  |                    | 0.01     | -10                | μΑ    |

| I <sub>DD1</sub> | V <sub>DD</sub> Supply Current During<br>CE "OFF"     | CE = −1V to +6V, Note 4                                                           |                    | 110      | 300                | μΑ    |

| I <sub>DD2</sub> | V <sub>DD</sub> Supply Current During<br>CE "ON"      | CE = V <sub>IHC</sub> , T <sub>A</sub> = 25°C                                     |                    | 20       | 40                 | mA    |

| OD AV1           | Average V <sub>DD</sub> Current                       | $T_{\Delta} = 25^{\circ} \text{C}$ Cycle Time = 400 ns, $t_{CE} = 230 \text{ ns}$ |                    | 35       | 60                 | m.A   |

| DD AV2           | Average V <sub>DD</sub> Current                       | Cycle Time = 1000 ns, t <sub>CE</sub> = 230 ns                                    | Ì                  | 15       | 30                 | mA    |

| leet             | V <sub>CC</sub> Supply Current During<br>CE "OFF"     | $CE = V_{ILC} \text{ or } \overline{CS} = V_{IH}$ , (Note 5)                      |                    | 0.01     | 10                 | μΑ    |

| I <sub>BB</sub>  | V <sub>BB</sub> Supply Current Average                |                                                                                   |                    | 5        | 100                | μΑ    |

| VIL              | Input Low Voltage                                     | t <sub>T</sub> = 20 ns (Figure 4)                                                 | -1.0               | <b>!</b> | 0.6                | · v   |

| V <sub>IH</sub>  | Input High Voltage                                    |                                                                                   | 2.4                |          | V <sub>cc</sub> +1 | · v   |

| VILC             | CE Input Low Voltage                                  |                                                                                   | -1.0               |          | 1.0                | v     |

| V <sub>IHC</sub> | CE Input High Voltage                                 |                                                                                   | V <sub>DD</sub> -1 | "        | V <sub>DD</sub> +1 | v     |

| VoL              | Output Low Voltage                                    | I <sub>OL</sub> = 2.0 mA                                                          | 0.0                |          | 0.45               | v     |

| V <sub>OH</sub>  | Output High Voltage                                   | I <sub>OH</sub> ≈ -2.0 mA                                                         | 2.4                |          | Vcc                | v     |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: The only requirement for the sequence of applying voltage to the device is that  $V_{DD}$ ,  $V_{CC}$ , and  $V_{SS}$  should never be 0.3V more negative than  $V_{BB}$ .

Note 3: Typical values are for  $T_A = 25^{\circ}$ C and nominal power supply voltages.

Note 4: The IDD and ICC currents flow to VSS. The IBB current is the sum of all leakage currents.

Note 5: During CE "ON" VCC supply current is dependent on output loading, VCC is connected to output buffer only.

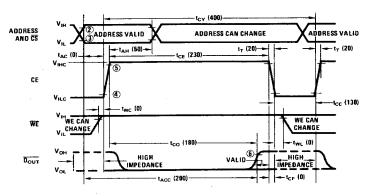

# AC Electrical Characteristics $T_A = 0^{\circ}C$ to +70°C, $V_{DD} = 12V \pm 10\%$ , $V_{CC} = 5V \pm 10\%$ , $V_{BB} = -5V \pm 10\%$

| SYMBOL           | PARAMETER                  | CONDITIONS                                                                                        | MIN | TYP | MAX      | UNITS |

|------------------|----------------------------|---------------------------------------------------------------------------------------------------|-----|-----|----------|-------|

| READ, WR         | ITE, READ/MODIFY/WRITE, AN | D REFRESH CYCLE                                                                                   |     | ·   | <u> </u> |       |

| t <sub>REF</sub> | Time Between Refresh       |                                                                                                   |     |     | 2        | ms    |

| t <sub>AC</sub>  | Address to CE Set-Up Time  | tAC is Measured From End of Address Transition                                                    | 0   |     |          | ns    |

| tan              | Address Hold Time          |                                                                                                   | 50  |     |          | ns    |

| tcc              | CE "OFF" Time              |                                                                                                   | 130 |     |          | ns    |

| t <sub>T</sub>   | CE Transition Time         |                                                                                                   | 10  |     | 40       | ns    |

| t <sub>CF</sub>  | CE "OFF" to Output High    |                                                                                                   |     |     |          | ns    |

|                  | Impedance State            |                                                                                                   |     |     |          |       |

| READ CYC         | LE                         |                                                                                                   |     |     |          |       |

| tcy              | Cycle Time                 |                                                                                                   | 400 |     |          | ns    |

| t <sub>CE</sub>  | CE "ON" Time               |                                                                                                   | 230 |     | 3000     | пs    |

| tco              | CE Output Delay            | $C_{LOAD}$ = 50 pF, Load = 1 TTL Gate, Ref = 2.0V,<br>$t_{ACC}$ = $t_{AC}$ + $t_{CO}$ + 1 $t_{T}$ |     |     | 180      | ns    |

| tACC             | Address to Output Access   |                                                                                                   |     |     | 200      | ns    |

| t <sub>WL</sub>  | CE to WE                   |                                                                                                   |     |     |          | ns    |

| twc              | WE to CE "ON"              |                                                                                                   | 0   |     |          | ns    |

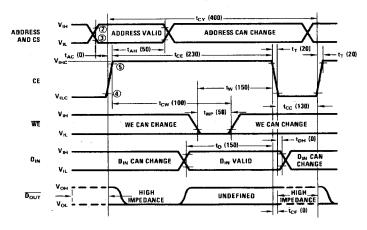

#### **AC Electrical Characteristics (Continued)**

$T_A = 0^{\circ}$ C to +70°C,  $V_{DD} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $V_{BB} = -5\% \pm 10\%$

| SYMBOL          | PARAMETER                    | CONDITIONS             | MIN   | TYP | MAX  | UNITS |

|-----------------|------------------------------|------------------------|-------|-----|------|-------|

| WRITE CYC       | ;LE                          |                        |       |     |      |       |

| t <sub>CY</sub> | Cycle Time                   |                        | 400   | 1   | 1    | ns    |

| t <sub>CE</sub> | CE "ON" Time                 |                        | 230   | 1   | 3000 | ns    |

| tw              | WE to CE "OFF"               |                        | 150   |     |      | ns    |

| tcw             | CE to WE                     | t <sub>T</sub> = 20 ns | 100   |     |      | ns    |

| t <sub>D</sub>  | D <sub>IN</sub> to CE Set-Up |                        | . 150 | İ   |      | ns    |

| t <sub>DH</sub> | D <sub>IN</sub> Hold Time    |                        | 0     |     |      | ns    |

| twe             | WE Pulse Width               |                        | 50    |     |      | ns    |

### **Switching Time Waveforms**

#### Write Cycle

Note 1: For refresh cycle, row and column addresses must be stable before t<sub>AC</sub> and remain stable for entire t<sub>AH</sub> period.

Note 2:  $V_{1L}$  max is the reference level for measuring timing of the address,  $\overline{\text{CS}}$  and  $D_{\text{IN}}$ .

Note 3:  $V_{IH}$  min is the reference level for measuring timing of the addresses,  $\overline{CS}$  and  $D_{IN}$ . Note 4:  $V_{SS}$  + 2.8V is the reference level for measuring timing of CE.

Note 4: V<sub>SS</sub> + 2.04 is the reference level for measuring timing of CE.

Note 5: V<sub>DD</sub> = 2V is the reference level for measuring timing of CE.

Note 6:  $V_{SS}$  + 2.0V is the reference level for measuring the timing of  $D_{OUT}$  for a high output.

1-51

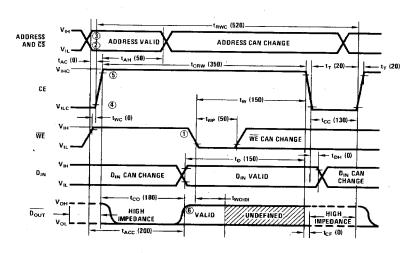

# **AC Electrical Characteristics** (Continued)

$T_A = 0^{\circ} C \text{ to } +70^{\circ} C$ ,  $V_{DD} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $V_{BB} = -5\% \pm 10\%$

| SYMBOL           | PARAMETER                             | CONDITIONS                                                                                                                      | MIN      | TYP | MAX  | UNITS |

|------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-----|------|-------|

| READ/MOD         | DIFY/WRITE CYCLE                      |                                                                                                                                 |          |     |      |       |

| <sup>t</sup> ewc | Read Modify Write (RMW)<br>Cycle Time |                                                                                                                                 | 520      |     | Ī    | ns    |

| tcsw             | CE Width During RMW                   |                                                                                                                                 | 350      |     | 3000 | ns    |

| twc              | WE to CE "ON"                         | •                                                                                                                               | 0        |     |      | ns    |

| tw               | WE to CE "OFF"                        |                                                                                                                                 | 150      |     | ļ    | ns    |

| twe              | WE Pulse Width                        | $t_T = 20 \text{ ns, } C_{LOAD} = 50 \text{ pF, Load} = 1 \text{ TTL Gate,}$<br>Ref = 2.0V, $t_{ACC} = t_{AC} + t_{CO} + 1 t_T$ | 50       |     | l    | ns    |

| t <sub>D</sub>   | D <sub>IN</sub> to CE Set-Up          | LOU, LACC LAC LEGO LIT                                                                                                          | 150      |     |      | ns    |

| toH              | D <sub>IN</sub> Hold Time             | İ                                                                                                                               | 0        |     |      | ns    |

| tco              | CE to Output Delay                    |                                                                                                                                 | -        | 1   | 180  | ns    |

| $t_{WO}$         | WE to D <sub>OUT</sub> Invalid        |                                                                                                                                 | 0        |     |      |       |

| tACC             | Access Time                           |                                                                                                                                 |          |     | 200  | กร    |

| CAPACITAN        | ICE (Note 1)                          | $T_A = 25^{\circ}C$                                                                                                             | <u> </u> | L   | L    |       |

| CAD              | Address Capacitance, CS               | V <sub>IN</sub> = V <sub>SS</sub>                                                                                               |          | 2   | [    | ρF    |

| $C_{CE}$         | CE Capacitance                        | V <sub>IN</sub> = V <sub>SS</sub>                                                                                               |          | 15  |      | рF    |

| $c_{out}$        | Data Output Capacitance               | V <sub>O∪7</sub> = 0V                                                                                                           |          | 5   |      | pF    |

| CIN              | D <sub>IN</sub> and WE Capacitance    | VIN = VSS                                                                                                                       |          | 4   |      | pF    |

Note 1: Capacitance measured with Boonton Meter or effective capacitance calculated from the equation  $C = I\Delta t/\Delta V$  with the current equal to a constant 20 mA.

## Switching Time Waveforms (Continued)

#### Read Modify Write Cycle

Note 1:  $\overline{WE}$  must be high until end of  $t_{CO}$ .

Note 2: V<sub>IL</sub> max is the reference level for measuring timing of the address, CS, D<sub>SN</sub> and WE.

Note 3:  $V_{IH}$  min is the reference level for measuring timing of the address,  $\overline{CS}$ ,  $D_{IN}$  and  $\overline{WE}$ .

Note 4: V<sub>SS</sub> + 2.0V is the reference level for measuring timing of CE.

Note 5:  $V_{DD} = 2V$  is the reference level for measuring timing of CE.

Note 6:  $V_{SS}$  + 2.0V is the reference level for measuring the timing of  $\overline{D_{OUT}}$  for a high output.