### **ADDRESSING MODES**

#### Row/Column

In this mode, the CRTC address lines (MA0-MA13) are generated as 8 column (MA0-MA7) and 6 row (MA8-MA13) addresses. Extra hardware is needed to compress this addressing into a straight binary sequence in order to conserve memory in the refresh RAM.

### **Binary**

In this mode, the CRTC address lines are straight binary and no compression circuits are needed. However, software complexity is increased since the CRT characters cannot be stored in terms of their row and column locations, but must be sequential.

### **USE OF DYNAMIC RAM FOR REFRESH MEMORY**

The R6545-1 permits the use of dynamic RAMS as storage devices for the Refresh RAM by continuing to increment memory addresses in the non-display intervals of the scan. This is a viable technique, since the Display Enable signal controls the actual video display blanking. Figure 2 illustrates Refresh RAM addressing for the case of binary addressing for 80 columns and 24 rows with 10 non-displayed columns and 10 non-displayed rows.

TOTAL = 90

|         |        |              |      |      | DISPLA | AY = 80 |      |      |      |      |     |      |

|---------|--------|--------------|------|------|--------|---------|------|------|------|------|-----|------|

|         | ſ      | ر إُت        | 1    | 2    | 3      | 76      | 77   | 78   | 79   | 80   | 81  | 89   |

|         | ١,     | 80           | 81   | 82   | 83     | 156     | 157  | 158  | 159  | 160  | 161 | 169  |

|         | 24     | 160          | 161  | 162  |        |         | 237  | 238  | 239  | 240  |     | 249  |

|         | Y = 2  | 240          | 241  | 242  |        |         | 317  | 318  | 319  | 320  |     | 329  |

| ≈ 34    | DISPLA | <del> </del> | ļ    | +    |        | -       |      |      |      |      |     | -    |

| I OI AL | ă      | 1680         | 1681 | 1682 |        |         | 1757 | 1758 | 1759 | 1760 |     | 1769 |

| 5       | 1      | 1760         | 1761 | 1762 |        |         | 1837 | 1838 | 1839 | 1840 |     | 1849 |

|         |        | 1840         | 1841 | 1842 |        |         | 1917 | 1918 | 1919 | 1920 |     | 1929 |

|         |        | 1920         | 1921 | 1922 |        |         | 1997 | 1998 | 1999 | 2000 |     | 2009 |

|         |        | 2000         | 2001 | 2002 |        |         | 2077 | 2078 | 2079 | 2080 |     | 2089 |

|         |        | 2640         | 2641 | 2642 |        | -       | 2717 | 2718 | 2720 |      |     | 2729 |

Figure 2. Memory Addressing Example (80 x 24)

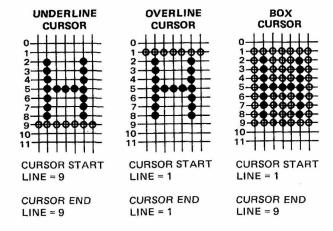

## **CURSOR OPERATION**

A one character wide cursor can be controlled by storing values into the Cursor Start Line (R10) and Cursor End Line (R11) registers and into the Cursor Position Address High (R14) and Cursor Position Low (R15) registers.

Bits 5 and 6 in the Cursor Start Line High Register (R10) control the cursor display and blink rate as follows:

| Bit 6 | Bit 5 | Cursor Operating Mode           |  |  |  |

|-------|-------|---------------------------------|--|--|--|

| 0     | 0     | Display Cursor Continuously     |  |  |  |

| 0     | 1     | Blank Cursor Continuously       |  |  |  |

| 1.    | 0     | Blink Cursor at 1/16 Field Rate |  |  |  |

| 1     | 1     | Blink Cursor at 1/32 Field Rate |  |  |  |

The cursor of up to 32 characters in height can be displayed on and between the scan lines as loaded into the Cursor Start Line (R10) and Cursor End Line (R11) Registers.

The cursor is positioned on the screen by loading the Cursor Position Address High (R14) and Cursor Position Address Low (R15) registers with the desired refresh RAM address. The cursor can be positioned in any of the 16K character positions. Hardware paging and data scrolling is thus allowed without loss of cursor position. Figure 3 is an example of the display cursor scan line.

Figure 3. Cursor Display Scan Line Control Examples

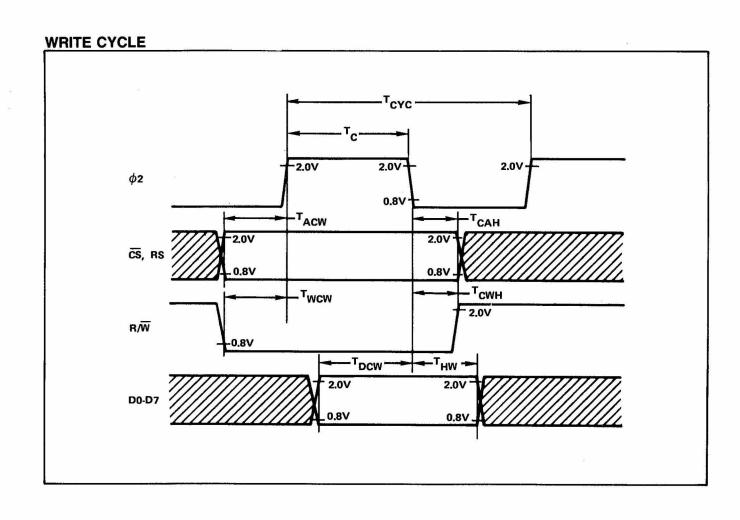

# MPU WRITE TIMING CHARACTERISTICS

$(V_{CC} = 5.0V \pm 5\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ unless otherwise noted})$

|                      |                  | 1 MHz |     | 2 MHz |     |      |

|----------------------|------------------|-------|-----|-------|-----|------|

| Characteristic       | Symbol           | Min   | Max | Min   | Max | Unit |

| Cycle Time           | TCYC             | 1.0   | _   | 0.5   | _   | μs   |

| Ø2 Pulse Width       | T <sub>C</sub>   | 440   | _   | 200   | _   | ns   |

| Address Set-Up Time  | TACW             | 180   | -   | 90    | _   | ns   |

| Address Hold Time    | TCAH             | 0     | _   | О     | _   | ns   |

| R/W Set-Up Time      | TWCW             | 180   | _   | 90    | _   | ns   |

| R/W Hold Time        | T <sub>CWH</sub> | 0     | -   | 0     | -   | ns   |

| Data Bus Set-Up Time | T <sub>DCW</sub> | 265   | .—  | 100   | _   | ns   |

| Data Bus Hold Time   | T <sub>HW</sub>  | 10    | -   | 10    | -   | ns   |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

# MPU READ TIMING CHARACTERISTICS

( $V_{CC} = 5.0V \pm 5\%$ ,  $T_A = 0$  to  $70^{\circ}$ C, unless otherwise noted)

|                                        |                  | 1   | MHz | 2 N |               |      |

|----------------------------------------|------------------|-----|-----|-----|---------------|------|

| Characteristic                         | Symbol           | Min | Max | Min | Max           | Unit |

| Cycle Time                             | TCYC             | 1.0 | _   | 0.5 | -             | μs   |

| Ø2 Pulse Width                         | T <sub>C</sub>   | 440 | -   | 200 |               | ns   |

| Address Set-Up Time                    | TACR             | 180 | -   | 90  | _             | ns   |

| Address Hold Time                      | TCAR             | 0   | -   | 0   | <b>ب</b> ـــه | ns   |

| R/W Set-Up Time                        | TWCR             | 180 |     | 90  |               | ns   |

| Read Access Time                       | TCDR             | _   | 340 | -   | 150           | ns   |

| Read Hold Time                         | THR              | 10  | -   | 10  | _             | ns   |

| Data Bus Active Time<br>(Invalid Data) | T <sub>CDA</sub> | 40  | -   | 40  | -             | ns   |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

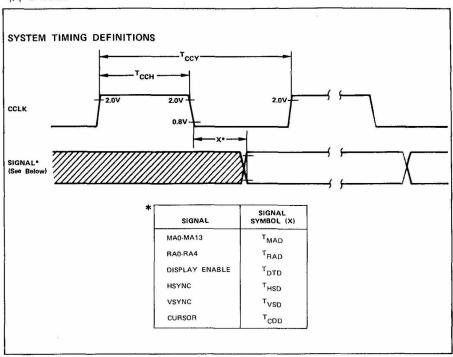

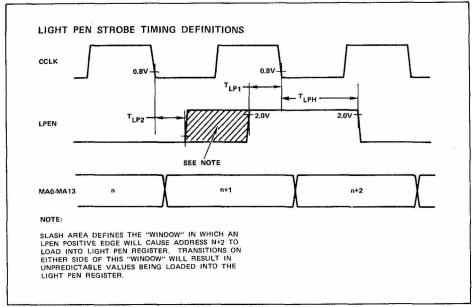

### **MEMORY AND VIDEO INTERFACE CHARACTERISTICS**

$(V_{CC} = 5.0V \pm 5\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ unless otherwise noted})$

|                            |                  | 1 MHz |     | 2 MHz |     |       |

|----------------------------|------------------|-------|-----|-------|-----|-------|

| Characteristics            | Symbol           | Min   | Max | Min   | Max | Units |

| Char, Clock Cycle Time     | TCCY             | 0.4   | 40  | 0.4   | 40  | μs    |

| Char, Clock Pulse Width    | тссн             | 200   | -   | 200   | - 1 | ns    |

| MA0-MA13 Propagation Delay | TMAD             |       | 300 |       | 300 | ns    |

| RA0-RA4 Propagation Delay  | TRAD             | -     | 300 | -     | 300 | ns    |

| DISPLAY ENABLE Prop. Delay | TDTD             | -     | 450 | -     | 450 | ns    |

| HYSNC Propagation Delay    | THSD             | -     | 450 | -     | 450 | ns    |

| VSYNC Propagation          | TVSD             | -     | 450 | _     | 450 | ns    |

| Cursor Propagation Delay   | TCDD             | - ,   | 450 | -     | 450 | ns    |

| LPEN Strobe Width          | TLPH             | 150   | -   | 150   | -   | ns    |

| LPEN to CCLK Delay         | T <sub>LP1</sub> | 20    |     | 20    |     | ns    |

| CCLK to LPEN Delay         | T <sub>LP2</sub> | 0     | -   | 0     | -   | ns    |

t<sub>r</sub>, t<sub>f</sub> = 20 ns (max)

## **SPECIFICATIONS**

### **Maximum Ratings**

| Rating                      | Symbol           | Value        | Unit |

|-----------------------------|------------------|--------------|------|

| Supply Voltage              | v <sub>cc</sub>  | -0.3 to +7.0 | Vdc  |

| Input Voltage               | V <sub>IN</sub>  | -0.3 to +7.0 | Vdc  |

| Operating Temperature Range | T <sub>OP</sub>  | 0 to +70     | °c   |

| Storage Temperature         | T <sub>STG</sub> | -55 to 150   | °c   |

All inputs contain protection circuitry to prevent damage due to high static discharges. Care should be taken to prevent unnecessary application of voltages in excess of the allowable limits.

### **Electrical Characteristics**

$(V_{CC} = 5.0V \pm 5\%, T_A = 0.70^{O}C, unless otherwise noted)$

| Characteristic                                   | Symbol          | Min | Max             | Unit         |

|--------------------------------------------------|-----------------|-----|-----------------|--------------|

| Input High Voltage                               | V <sub>IH</sub> | 2.0 | v <sub>cc</sub> | Vdc          |

| Input Low Voltage                                | V <sub>IL</sub> | 0.3 | 0.8             | Vdc          |

| Input Leakage (Ø2, R/W, RES, CS, RS, LPEN, CCLK) | IN              | _   | 2.5             | <b>µ</b> Adc |

| Three-State Input Leakage (D0-D7)                |                 |     |                 |              |

| $(V_{IN} = 0.4 \text{ to } 2.4V)$                | ITSI            | _   | 10.0            | <b>µ</b> Adc |

| Output High Voltage                              |                 |     |                 | 2<br>9       |

| $I_{LOAD} = 205 \ \mu Adc (D0-D7)$               | v <sub>он</sub> | 2.4 | -               | Vdc          |

| $I_{LOAD} = 100 \ \mu Adc (all others)$          |                 |     |                 |              |

| Output Low Voltage                               |                 |     |                 |              |

| I <sub>LOAD</sub> = 1.6 mAdc                     | V <sub>OL</sub> | _   | 0.4             | Vdc          |

| Power Dissipation                                | PD              | _   | 1000            | mW           |

| Input Capacitance                                |                 |     |                 |              |

| Ø2, R/W, RES, CS, RS, LPEN, CCLK                 | CIN             | _   | 10.0            | pF           |

| D0-D7                                            | , "             | _   | 12.5            | pF           |

| Output Capacitance                               | СООТ            | -   | 10.0            | pF           |

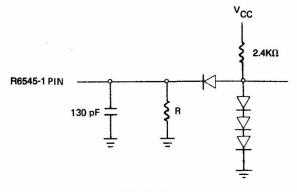

## **TEST LOAD**

$\begin{array}{l} \text{R=11K}\Omega \; \text{FOR D0-D7} \\ = & \text{24K}\Omega \; \text{FOR ALL OTHER OUTPUTS} \end{array}$