# 2108-2 AND 2108-4 8192 X 1 BIT DYNAMIC RAM

| •                            | 2108-2      | 2108-4      |

|------------------------------|-------------|-------------|

|                              | S1572,S1573 | S1626,S1627 |

| Max. Access Time (ns)        | 200         | 300         |

| Read, Write Cycle (ns)       | 350         | 425         |

| Read-Modify-Write Cycle (ns) | 400         | 595         |

- 8K RAM in Industry Standard 16 Pin Package

- **Low Standby Power**

- All Inputs Including Clocks TTL Compatible

- Standard Power Supplies +12V, +5V, -5V

- Only 64 Refresh Cycles Required Every 2 ms

- On-Chip Input Latches

- Output is Three-State, TTL Compatible;

Data is Latched and Valid into Next Cycle

- Fully Compatible with 4K and 16K Dynamic RAMs

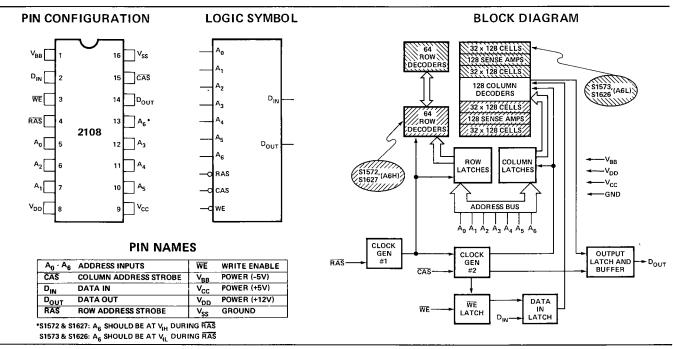

The Intel® 2108 is a 8K Dynamic MOS RAM organized as 8192 words by 1 bit. The 2108 employs the same masks and highly reliable, production-proven two layer polysilicon N-MOS technology as the intel® 2116 16K RAM. As shown in the block diagram below, the 2116 is organized as two 8K RAMs on a single shoon die Each of these 8K RAMs contains its own row decoders, sense amplifiers, and storage cells. The 2108 is fully tested to insure that one 8K RAM meets all AC and DC specifications.

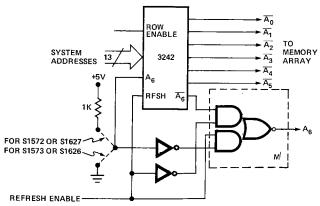

The 2108 is available as either the upper or lower half of the 2116. Address  $A_6$  selects the operating half. For S1572 or S1627,  $A_6$  should be high ( $V_{IH}$ ) during row address strobe (RAS). For S1573 or S1626,  $A_6$  should be low ( $V_{IL}$ ) during RAS. The use of the Intel® 3242 Address Multiplexer/Refresh Counter with a 2108 is described on page 2-66. The 2108 is packaged in the industry standard 16-pin DIP which is compatible with widely available automated handling equipment and facilitates easy upgrading from 2104A-type 4K RAM Systems and up to 2116-type 16K RAM Systems.

As in the 2104A-type 4K RAM and 2116-type 16K RAM, the 2108 has non-critical clock timing requirements which allow use of addressing multiplexing while maintaining high performance. Three methods of refreshing are permissable; they are described in the applications section of this data sheet.

The 2108 will provide the same reliable operation in its system usage as any Intel product. Information on the details of reliability tests performed on the 2108 and field data on the use of partial devices are available from Intel Corporation.

## **Absolute Maximum Ratings\***

| Ambient Temperature Under Bias10°C to +80°     | °C |

|------------------------------------------------|----|

| Storage Temperature65°C to +150°               | °C |

| Voltage on any Pin Relative to V <sub>BB</sub> |    |

| $(V_{SS} - V_{BB} \ge 4V)$ 0.3V to +20         | J۷ |

| Power Dissipation                              | ξW |

#### \*COMMENT:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. and Operating Characteristics [1],[2]

$T_{A} = 0^{\circ} C$  to  $70^{\circ} C$ ,  $V_{DD} = +12 V \pm 10\%$ ,  $V_{CC} = +5 V \pm 10\%$ ,  $V_{BB} = -5 V \pm 10\%$ ,  $V_{SS} = 0 V$ , unless otherwise noted.

| Symbol               |                                                 | Limits                |                     |                    |      |                                                             |                                  |                          |  |

|----------------------|-------------------------------------------------|-----------------------|---------------------|--------------------|------|-------------------------------------------------------------|----------------------------------|--------------------------|--|

|                      | Parameter                                       | Min.                  | Typ. <sup>(3)</sup> | Max.               | Unit | Conditions                                                  |                                  |                          |  |

| ILI                  | Input Load Current (any input)                  |                       |                     | .10                | μΑ   | V <sub>IN</sub> = V <sub>IL MIN</sub> to V <sub>IH MA</sub> | X                                |                          |  |

| I <sub>LO</sub>      | Output Leakage Current for high impedance state |                       | 0.1                 | 10                 | μΑ   | Chip deselected: RAS and V <sub>OUT</sub> = 0 to 5.5V       | I CAS at V <sub>IH</sub>         |                          |  |

| $I_{DD1}$            | V <sub>DD</sub> Supply Current                  |                       | 1.2                 | 2                  | mA   | CAS and RAS at V <sub>IH</sub> or CAS-only                  |                                  |                          |  |

| I <sub>BB1</sub>     | V <sub>BB</sub> Supply Current                  |                       | 1                   | 50                 | μΑ   | cycle. Chip deselected prior to measurement. See Note 5.    |                                  |                          |  |

| I <sub>DD2</sub> [4] | Operating V <sub>DD</sub> Current               |                       | 53                  | 69                 | mA   | 2108-2 t <sub>CYC</sub> = 350 ns                            | T <sub>A</sub> = 25°C<br>Device  |                          |  |

|                      |                                                 | Operating VDD Current |                     | 49                 | 65   | mA                                                          | 2108-4 t <sub>CYC</sub> = 425 ns | selected.<br>See Note 6. |  |

| I <sub>BB2</sub>     | Operating V <sub>BB</sub> Current               |                       | 120                 | 400                | μΑ   | Device selected                                             | <u> </u>                         |                          |  |

| [CC1 <sup>[7]</sup>  | V <sub>CC</sub> Supply Current when deselected  |                       |                     | 10                 | μΑ   |                                                             |                                  |                          |  |

| V <sub>IL</sub>      | Input Low Voltage (any input)                   | -1.0                  |                     | 0.8                | V    |                                                             |                                  |                          |  |

| V <sub>IH</sub>      | Input High Voltage (any input)                  | 2.4                   |                     | V <sub>CC</sub> +1 | V    |                                                             |                                  |                          |  |

| V <sub>OL</sub>      | Output Low Voltage                              | 0.0                   |                     | 0.4                | V    | I <sub>OL</sub> = 4.1 mA (Read Cycle                        | e Only)                          |                          |  |

| V <sub>OH</sub>      | Output High Voltage                             | 2.4                   |                     | V <sub>CC</sub>    | V    | I <sub>OH</sub> = -5 mA (Read Cycle                         | Only)                            |                          |  |

# **Capacitance** [8] $T_A = 25^{\circ}C$ , $V_{DD} = 12V \pm 10\%$ , $V_{CC} = 5V \pm 10\%$ , $V_{BB} = -5V \pm 10\%$ , $V_{SS} = 0V$ , unless otherwise noted.

| Symbol          | Parameter                         | Тур. | Max. | Unit | Conditions                        |

|-----------------|-----------------------------------|------|------|------|-----------------------------------|

| C <sub>I1</sub> | Address, Data In & WE Capacitance | 4    | 7    | pF   | V <sub>IN</sub> = V <sub>SS</sub> |

| C <sub>I2</sub> | RAS Capacitance                   | 3    | 5    | pF   | V <sub>IN</sub> = V <sub>SS</sub> |

| C <sub>I3</sub> | CAS Capacitance                   | 6    | 10   | pF   | V <sub>IN</sub> = V <sub>SS</sub> |

| co              | Data Output Capacitance           | 3    | 7    | pF   | V <sub>OUT</sub> = OV             |

#### Notes

- 1. All voltages referenced to VSS. No power supply sequencing is required but VDD, VCC, and VSS should never be 0.3V or more negative than VBB.

- 2. To avoid self-clocking, RAS should not be allowed to float.

- 3. Typical values are for  $T_A = 25^{\circ}$  C and nominal power supply voltages.

- 4. For RAS-only refresh IDD = 0.78 IDD2. For CAS-before-RAS (64 cycle refresh) IDD = 0.96 IDD2.

- 5. The chip is deselected (i.e., output is brought to high impedance state) by CAS-only cycle or by CAS-before RAS cycle. The current flowing in a selected (i.e., output on) chip with RAS and CAS at VIH is approximately twice IDD1.

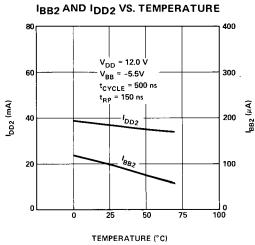

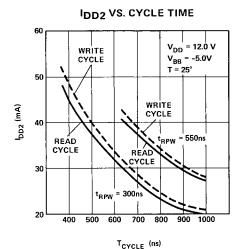

- 6. See Page 2-62 for typical  $I_{\mbox{\scriptsize DD}}$  characteristics under other conditions.

- 7. When chip is selected VCC supply current is dependent on output loading; VCC is connected to output buffer only.

- 8. Capacitance measured with Boonton Meter.

#### TYPICAL CHARACTERISTICS

Figure 1.

Figure 2.

#### **Standby Power Calculations:**

$$P_{REF} = P_{OP} \left(N \frac{t_{CYC}}{t_{REF}}\right) + P_{SB} \left(1 - N \frac{t_{CYC}}{t_{REF}}\right)$$

where

$P_{OP}$  = Power dissipation – continuous operation =  $V_{DD} \times I_{DD2}$ .

N = Number of refresh cycles (64).

$t_{CYC}$  = Cycle time for a refresh cycle.

t<sub>REF</sub> = Time between refreshes

$P_{SB}$  = Standby power dissipation =  $V_{DD} \times I_{DD1} + |V_{BB}| \times I_{BB}$

Note that I<sub>DD2</sub> depends upon refresh as follows:

- 1. For  $(\overline{RAS} \text{ before } \overline{CAS})$  use  $I_{DD2}$  from Figures 1 and 2.

- 2. For (CAS before RAS) multiply IDD2 determined in (1) by 0.96.

- 3. For (RAS only) multiply IDD2 determined in (1) by 0.78.

Examples of typical calculations for  $V_{BB}$  = -5.0V,  $V_{DD}$  = 12.0V,  $T_A$  = 25°C,  $t_{CYC}$  = 0.425  $\mu$ s,  $t_{RAS}$  = 0.3  $\mu$ s.  $t_{REF}$  = 2000  $\mu$ s:

1. 128 cycle ( $\overline{RAS}$  before  $\overline{CAS}$ ):  $P_{OP}$  = 12.0V x 43 mA = 516 mW

$$P_{REF} = 516 (128 \frac{0.425}{2000}) + (12x1.2+5x0.001) (1-128 \frac{0.425}{2000})$$

$P_{REF} = 28.0 \text{ mW}$

2. 64 cycle ( $\overline{CAS}$  before  $\overline{RAS}$ );  $P_{OP}$  = 12.0V x 43 (0.96) mA = 495 mW.

$$P_{REF} = 495 (64 \frac{0.425}{2000}) + (12x1.2+5x0.001) (1-64 \frac{0.425}{2000}) =$$

$P_{RFF} = 20.9 \text{ mW}$

3. 128 cycle ( $\overline{RAS}$  only):  $P_{OP}$  = 12.0V x 43 (0.78) mA = 402 mW  $P_{REF}$  = 25.0 mW

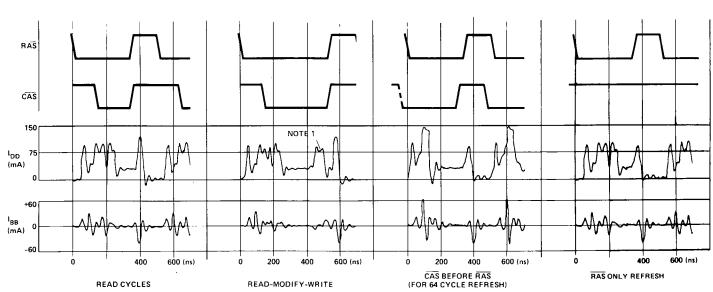

Note 1: Increase in current due to  $\overline{WE}$  going low. Width of this current pulse is independent of  $\overline{WE}$  pulse width.

Figure 3. Supply Current Waveforms.

# A.C. Characteristics

$T_A = 0^{\circ}C \text{ to } 70^{\circ}C, \ V_{DD} = 12V \pm 10\%, \ V_{CC} = 5V \pm 10\%, \ V_{BB} = -5V \pm 10\%, \ V_{SS} = 0V, \ \text{unless otherwise noted}.$

### READ, WRITE, READ-MODIFY-WRITE AND REFRESH CYCLES

| Symbol Parameter                |                                   | 2108 |      |      | 2108-4 |      |

|---------------------------------|-----------------------------------|------|------|------|--------|------|

|                                 | Parameter                         | Min. | Max. | Min. | Max.   | Unit |

| t <sub>REF</sub>                | Time Between Refresh              |      | 2    |      | 2      | ms   |

| t <sub>RP</sub>                 | RAS Precharge Time                | 75   |      | 95   |        | ns   |

| t <sub>CP</sub>                 | CAS Precharge Time                | 100  |      | 125  |        | ns   |

| t <sub>RCL</sub> [2]            | RAS to CAS Leading Edge Lead Time | 45   | 75   | 60   | 110    | ns   |

| t <sub>CRP</sub> [3]            | CAS to RAS Precharge Time         | 0    |      | 0    |        | ns   |

| t <sub>RSH</sub>                | RAS Hold Time                     | 160  |      | 220  |        | ns   |

| <sup>t</sup> CSH                | CAS Hold Time                     | 200  |      | 300  |        | ns   |

| t <sub>ASR</sub>                | Row Address Set-Up Time           | . 0  |      | 0    |        | ns   |

| t <sub>ASC</sub>                | Column Address Set-Up Time        | -10  |      | -10  |        | ns   |

| t <sub>AH</sub>                 | Address Hold Time                 | 45   |      | 60   |        | ns   |

| t <sub>T</sub>                  | Transition Time (Rise and Fall)   |      | 50   |      | 50     | ns   |

| t <sub>OFF</sub>                | Output Buffer Turn Off Delay      | 0    | 60   | 0    | 80     | ns   |

| t <sub>CAC</sub> <sup>[4]</sup> | Access Time From CAS              |      | 125  |      | 190    | ns   |

| t <sub>RAC</sub> [4]            | Access Time From RAS              |      | 200  |      | 300    | ns   |

#### **READ AND REFRESH CYCLES**

|                                 |                                    | 2108 |       |      | 2108-4        |      |

|---------------------------------|------------------------------------|------|-------|------|---------------|------|

| Symbol                          | Parameter                          | Min. | Max.  | Min. | Max.          | Unit |

| t <sub>CYC</sub> <sup>[5]</sup> | Random Read Cycle Time             | 350  |       | 425  |               | ns   |

| t <sub>RAS</sub>                | RAS Pulse Width                    | 275  | 32000 | 330  | 32000         | ns   |

| t <sub>CAS</sub>                | CAS Pulse Width                    | 125  | 3000  | 190  | 3000          | ns   |

| t <sub>CH</sub>                 | CAS Hold Time for RAS-Only Refresh | 30   |       | 30   | -             | ns   |

| t <sub>CPR</sub>                | CAS Precharge for 64 Cycle Refresh | 30   | ···   | 30   | <del></del> - | ns   |

| t <sub>RCH</sub>                | Read Command Hold Time             | 20   |       | 20   | <del>,</del>  | ns   |

| t <sub>RCS</sub>                | Read Command Set-Up Time           | 0    |       | 0    |               | ns   |

| t <sub>DOH</sub>                | Data-Out Hold Time                 | 32   |       | 32   |               | μs   |

#### **WRITE CYCLE**

| Symbol Parameter                |                                | 2108-2 |       |      | 2108-4 |    |

|---------------------------------|--------------------------------|--------|-------|------|--------|----|

|                                 | , Min.                         | Max.   | Min.  | Max. | Unit   |    |

| t <sub>CYC</sub> <sup>[5]</sup> | Random Write Cycle Time        | 350    |       | 425  |        | ns |

| t <sub>RAS</sub>                | RAS Pulse Width                | 275    | 32000 | 330  | 32000  | ns |

| t <sub>CAS</sub>                | CAS Pulse Width                | 125    | 10000 | 190  | 10000  | ns |

| twch                            | Write Command Hold Time        | 75     |       | 100  |        | ns |

| t <sub>WP</sub>                 | Write Command Pulse Width      | 50     |       | 100  |        | ns |

| t <sub>RWL</sub>                | Write Command to RAS Lead Time | 125    |       | 200  |        | ns |

| t <sub>CWL</sub>                | Write Command to CAS Lead Time | 100    |       | 160  |        | ns |

| t <sub>DS</sub> [6]             | Data-In Set-Up Time            | 0      |       | 0    |        | ns |

| t <sub>DH</sub> [6]             | Data-In Hold Time              | 100    |       | 125  | ,      | ns |

Notes: 1. All voltages referenced to VSS.

- 2. CAS must remain at V<sub>IH</sub> a minimum of t<sub>RCL MIN</sub> after RAS switches to V<sub>IL</sub>. To achieve the minimum guaranteed access time (t<sub>RAC</sub>), CAS must switch to V<sub>IL</sub> at or before t<sub>RCL</sub> (MAX) = t<sub>RAC</sub> -t<sub>CAC</sub>. Device operation is not guaranteed for t<sub>RCL</sub>>2 µs.

- 3. The tCRP specification is less restrictive than the tCRL range which was specified in the 2108 preliminary data sheet.

- 4. Load = 1 TTL and 50 pF.

- 5. The minimum cycle timing does not allow for t<sub>T</sub> or skews.

- 6. Referenced to CAS or WE, whichever occurs last.

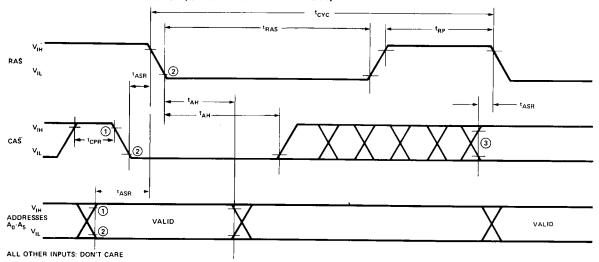

# **Waveforms**

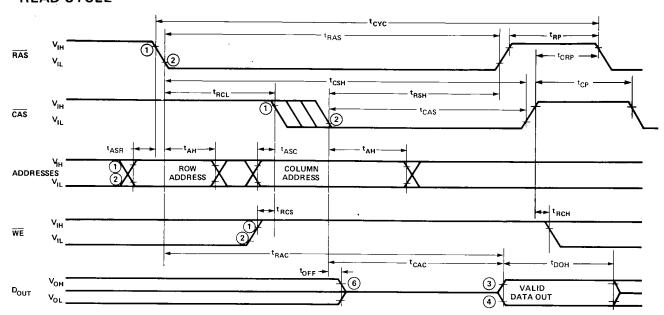

### **READ CYCLE**

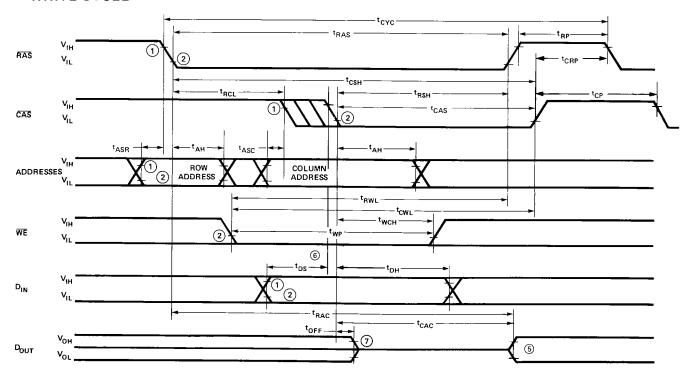

### **WRITE CYCLE**

Notes:

- VIH MIN and VIL MAX are reference levels for measuring timing of input signals.

VOH MIN and VOL MAX are reference levels for measuring timing of DOUT.

DOUT follows DIN when writing, with WE before CAS.

Referenced to CAS or WE, whichever occurs last.

- - 7. topp is measured to  $I_{OUT} \leq |I_{LO}|$ .

# A.C. Characteristics

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{DD} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $V_{BB} = -5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

#### **READ-MODIFY-WRITE CYCLE**

|                  | 21                             | 2108-2 |       | 2108-4 |                                       |      |

|------------------|--------------------------------|--------|-------|--------|---------------------------------------|------|

| Symbol           | Parameter                      | Min.   | Max.  | Min.   | Max.                                  | Unit |

| t <sub>RMW</sub> | Read-Modify-Write Cycle Time   | 400    |       | 595    |                                       | ns   |

| t <sub>CRW</sub> | RMW Cycle CAS Width            | 225    | 3000  | 350    | 3000                                  | ns   |

| t <sub>RRW</sub> | RMW Cycle RAS Width            | 325    | 32000 | 500    | 32000                                 | ns   |

| t <sub>RWH</sub> | RMW Cycle RAS Hold Time        | 250    |       | 390    |                                       | ns   |

| t <sub>CWH</sub> | RMW Cycle CAS Hold Time        | 300    |       | 460    |                                       | ns   |

| t <sub>RWL</sub> | Write Command to RAS Lead Time | 125    |       | 200    |                                       | ns   |

| t <sub>CWL</sub> | Write Command to CAS Lead Time | 100    |       | 160    | · · · · · · · · · · · · · · · · · · · | ns   |

| t <sub>WP</sub>  | Write Command Pulse Width      | 50     |       | 100    | -                                     | ns   |

| t <sub>RCS</sub> | Read Command Set-Up Time       | 0      |       | 0      |                                       | ns   |

| t <sub>MOD</sub> | Modify Time                    | 0      | 10    | 0      | 10                                    | μs   |

| t <sub>DS</sub>  | Data-In Set-Up Time            | 0      |       | 0      |                                       | ns   |

| t <sub>DHM</sub> | Data-In Hold Time (RMW Cycle)  | 50     |       | 125    |                                       | ns   |

# **Waveforms**

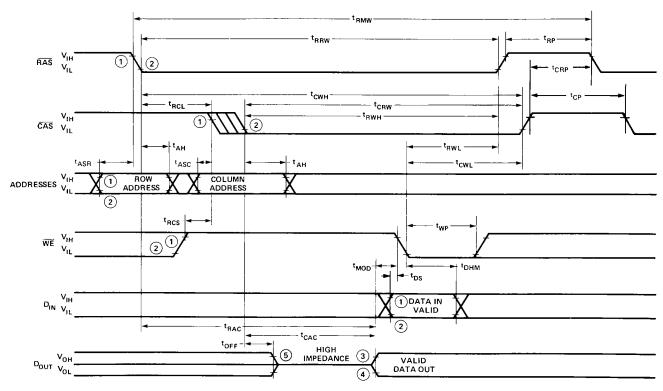

#### **READ MODIFY WRITE CYCLE**

Notes: 1,2.  $V_{IHMIN}$  and  $V_{ILMAX}$  are reference levels for measuring timing of input signals.

- 3,4.  $V_{OHMIN}$  and  $V_{OLMAX}$  are reference levels for measuring timing of  $D_{OUT}$ .

- 5. toff is measured to  $I_{OUT} \leq |I_{LO}|$ .

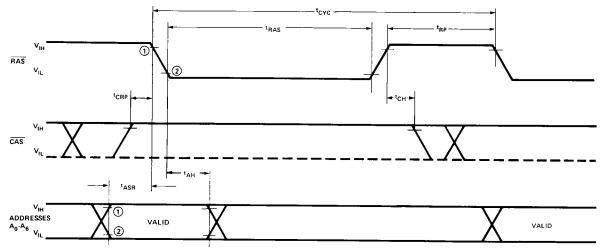

## **Refresh Cycle Waveforms**

# CAS BEFORE RAS CYCLES. (64 CYCLE REFRESH)

### RAS ONLY CYCLES (128 CYCLE REFRESH)

Notes: 1,2. VIHMIN and VILMAX are reference levels for measuring timing of input signals.

.3. CAS must be high or low as appropriate for the next cycle.

# **Applications Information**

The 2108 may be refreshed in any of three modes: read cycles with  $\overline{RAS}$  before  $\overline{CAS}$  timing as shown on page 5,  $\overline{RAS}$  only cycles (page 7), or  $\overline{CAS}$  before  $\overline{RAS}$  cycles (page 7). In all three modes A<sub>6</sub> must be held high for the S1572 and S1627 or low for the S1573 and S1626. The row addressed by A<sub>0</sub> through A<sub>5</sub> is refreshed. Therefore, 64 cycles are required to refresh the stored data.

The CAS-before-RAS mode is useful in the 2116 as a technique for increasing memory availability and minimizing standby power dissipation by requiring only 64 refresh cycles every 2 ms. Systems employing the 2108 in a CAS-before-RAS refresh mode can be easily upgraded to the most efficient 16K RAM capability.

Since the 2108 input pin  $A_6$  supplies two system addresses ( $A_6$  and  $A_{13}$ ) to the internal memory array, it is not possible to simply tie this input high or low. The 2108 input  $A_6$  must be tied to the appropriate level only during row address strobe ( $\overline{RAS}$ ) and then used to supply the high order system address  $A_{13}$  during column address strobe ( $\overline{CAS}$ ). Control of  $A_6$  in a system may be implemented. as shown at right. In this circuit the output  $A_6$  of multiplexer M

supplies the appropriate high or low level (determined by S1572, S1627, S1573, or S1626) during RAS for both a memory cycle and refresh cycle. During CAS, system address A13 is multiplexed on A6 as shown. See the 2116 section for additional applications information.

# Power Supply Decoupling/ Distribution

Power supply current waveforms for the 2108 are shown in Figure 3. The  $V_{DD}$  supply provides virtually all of the operating current for the 2108. The VDD supply current, IDD, has two components: transient current peaks when the clocks change state and a DC component while the clocks are active (low). When selecting the decoupling capacitors for the  $V_{\mbox{\scriptsize DD}}$  supply, the characteristics of capacitors as well as the current waveform must be considered. Suppression of transient or pulse currents require capacitors with small physical size and low inherent inductance. Monolithic and other ceramic capacitors exhibit these desirable characteristics. When the current waveform indicates a DC component, bulk capacity must be located near the current load to supply the load power. Inductive effects of PC board traces and bus bars preclude supplying the DC component from bulk capacitors at the periphery of a memory matrix without voltage droop during the active portion of a memory cycle. This means that some bulk capacity in the form of electrolytic or large ceramic capacitors should be distributed around or within the memory matrix.

The  $V_{BB}$  supply current,  $I_{BB}$ , has high transient current peaks, with essentially no DC component (less than 400 microamperes). The  $V_{BB}$  capacitors should be selected for transient suppression characteristics. The following capacitance values and locations are recommended for the 2108:

- A 0.33 µF ceramic capacitor between V<sub>DD</sub> and V<sub>SS</sub> (ground) at every other device.

- 2. A 0.1  $\mu$ F ceramic capacitor between V<sub>BB</sub> and V<sub>SS</sub> at every other device (preferably alternate devices to the V<sub>DD</sub> decoupling above).

- A 4.7 μF electrolytic capacitor between V<sub>DD</sub> and V<sub>SS</sub> for each eight devices and located adjacent to the devices.

The V<sub>CC</sub> supply is connected only to the 2108 output buffer and is not used internally. The load current from the V<sub>CC</sub> supply is dependent only upon the output loading and is usually only the input high level current to a TTL gate and the output leakage currents of any OR-tied 2108 (typically 100  $\mu\text{A}$  or less total). Intel recommends that a 0.1 or 0.01  $\mu\text{F}$  ceramic capacitor be connected between V<sub>CC</sub> and V<sub>SS</sub> for every eight devices to preclude coupled noise from affecting the TTL devices in the system.

Intel recommends a power supply distribution system such that each power supply is grided both horizontally and vertically at each memory device. This technique minimizes the power distribution system impedance and enhances the effect of the decoupling capacitors.

## **Output Data Latch**

The 2108 contains an output data latch eliminating the need for an external system data latch and the timing circuitry required to strobe an external latch. The output latch operates identically to the 16-pin 4K RAM (Intel 2104) output latch enhancing the system compatibility of the 16K and 4K devices.

Operation of the output latch is controlled by CAS. The data output will go to the high-impedance state immediately following the CAS leading edge during each data cycle and will either go to valid data at access time on selected devices (devices receiving both RAS and CAS) or will remain in the high impedance state on unselected devices (devices receiving only CAS). During RAS-only refresh cycles, the data output remains in the state it was prior to the RAS-only cycle. This unique feature of latched output RAMs allows a refresh cycle to be hidden among data cycles without impacting data availability. For instance, a RAS-only refresh cycle could follow each data cycle in a microprocessor system but the accessed data would remain at the device output and the microprocessor could take the data at any time within the cycle. Non-latched output devices do not provide this type of hidden refresh capability since their data output would go to the high impedance state at the end of the data cycle.

## **Page Mode Operation**

The 2108 is designed for page mode operation and is presently being characterized for that mode. Specifications will be available at a later date.

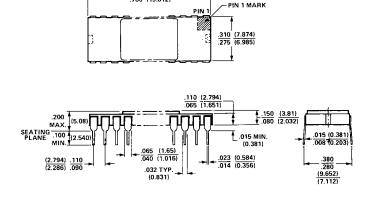

# **Packaging Information**

16-LEAD HERMETIC DUAL IN-LINE PACKAGE