# M27C256/E27C256 256K CMOS EPROM

November 1989

# Features

■ 256K (32K x 8) CMOS EPROM

Seeg

- Military and Extended Temperature Range -55°C to +125°C: M27C256

- -40°C to +85°C; E27C256

- Ultra Low Power 150 µA Max. V<sub>cc</sub> Standby Current 50 mA Max. Active Current

- Programmed Using Intelligent Algorithm • 12.5 V V ...

- 200 ns Access Times

- 5V±10%V<sub>cc</sub>

- JEDEC Approved Bytewide Pin Configuration

- Silicon Signature®

# Description

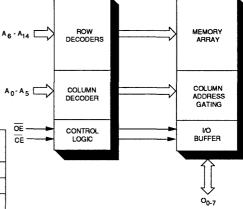

SEEQ's 27C256 is the industry's first 256K CMOS EPROM. It has a 32K x 8 organization and has very low power dissipation. Its active current is less than one half the active power of n-channel EPROMs. In addition the standby current is orders of magnitude lower than those

# Mode Selection

| PINS               | CE<br>(20)      | 0E<br>(22)      | V <sub>PP</sub><br>(1) | V <sub>cc</sub><br>(28) | Outputs<br>(11-13, 15-19) |

|--------------------|-----------------|-----------------|------------------------|-------------------------|---------------------------|

| Read               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>cc</sub>        | V <sub>cc</sub>         | D <sub>out</sub>          |

| Output Disable     | Х               | V <sub>IH</sub> | V <sub>cc</sub>        | V <sub>cc</sub>         | High Z                    |

| Standby            | V <sub>IH</sub> | Х               | V <sub>cc</sub>        | V <sub>cc</sub>         | High Z                    |

| Program            | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>pp</sub>        | V <sub>cc</sub>         | D <sub>in</sub>           |

| Program Verify     | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>PP</sub>        | V <sub>cc</sub>         | D <sub>out</sub>          |

| Program Inhibit    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>PP</sub>        | V <sub>cc</sub>         | High Z                    |

| Silicon Signature* | V <sub>IL</sub> | V <sub>iL</sub> | V <sub>cc</sub>        | V <sub>cc</sub>         | Encoded<br>Data           |

X can be either  $V_{\mu}$  or  $V_{\mu}$ \*For Silicon Signature:  $A_0$  is toggled,  $A_3$  = 12V, and all other addresses are at a TTL low.

Silicon Signature is a registered trademark of SEEQ Technology, Inc.

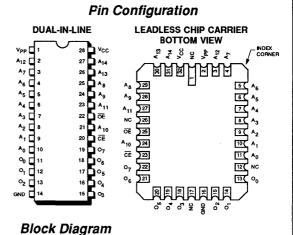

# Pin Names

| $A_0 - A_5$                     | ADDRESSES – COLUMN (LSB) |

|---------------------------------|--------------------------|

| $A_{6} - A_{14}$                | ADDRESSES - ROW          |

| CE                              | CHIP ENABLE              |

| ŌĒ                              | OUTPUT ENABLE            |

| 0 <sub>0</sub> - 0 <sub>7</sub> | OUTPUTS                  |

| NC                              | NO CONNECT               |

same EPROMs. Consequently, system memory sizes can be substantially increased at a very small increase in power. Low active and standby power is important in applications which require portability, low cooling cost, high memory bit density, and long term reliability.

The 27C256 is specified over both the extended and miltary temperature ranges at 5 V  $\pm$  10% V  $_{cc}$  . The access time is specified at 200 ns, making the 27C256 compatible with most of today's microprocessors. Its inputs and outputs are completely TTL compatible.

### Absolute Maximum Ratings

| Temperature |

|-------------|

|-------------|

| Storage                                | –65°C to +150°C   |

|----------------------------------------|-------------------|

| M27C256 Under Bias                     |                   |

| E27C256 Under Bias                     | –50°C to +95°C    |

| All Inputs or Outputs                  |                   |

| with Respect to Ground                 | +7 V to -0.6 V    |

| V <sub>PP</sub> with Respect to Ground | +14.0 V to -0.6 V |

| Voltage on A                           |                   |

| with Respect to Ground                 | +14.0 V to -0.6 V |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

|                                                   | M27C256-20, M27C256-25<br>M27C256-30 | E27C256-20, E27C256-25<br>E27C256-30 |

|---------------------------------------------------|--------------------------------------|--------------------------------------|

| V <sub>cc</sub> Supply Voltage <sup>[1]</sup>     | 5V ± 10%                             | 5V ± 10%                             |

| Temperature Range (Read Mode)                     | (Case) -55°C to +125°C               | (Ambient) -40°C to +85°C             |

| V <sub>PP</sub> During Read <sup>[2]</sup>        | V <sub>cc</sub>                      | V <sub>cc</sub>                      |

| V <sub>PP</sub> During Programming <sup>[3]</sup> | 12.5 ± 0.3V                          | 12.5 ± 0.3V                          |

# DC Operating Characteristics During Read or Programming

|                                |                                                                          | Limits |                     |                |                                                                                                                      |  |

|--------------------------------|--------------------------------------------------------------------------|--------|---------------------|----------------|----------------------------------------------------------------------------------------------------------------------|--|

| Symbol                         | Parameter                                                                | Min.   | Max.                | Units          | Test Condition                                                                                                       |  |

| I <sub>IN</sub> <sup>[4]</sup> | Input Leakage                                                            |        | 1                   | μA             | V <sub>IN</sub> = V <sub>cc</sub> Max.                                                                               |  |

| 0 <sup>[5]</sup>               | Output Leakage                                                           |        | 10                  | μA             | V <sub>out</sub> = V <sub>cc</sub> Max.                                                                              |  |

| PP                             | V <sub>PP</sub> Current<br>Standby Mode<br>Read Mode<br>Programming Mode |        | 150<br>1<br>30      | μA<br>mA<br>mA | $\overline{CE} = V_{cc} - 1 \text{ v. min.}$ $F = 5 \text{ MHz, } \overline{CE} = V_{IL}$ $V_{PP} = 12.5 \text{ v.}$ |  |

|                                | V <sub>cc</sub> Standby Current                                          |        | 150                 | μA             | $\overline{CE} \ge V_{cc} - 1 v.$                                                                                    |  |

| ccz                            | V <sub>cc</sub> Standby Current                                          |        | 2                   | mA             | CE = V <sub>IH</sub>                                                                                                 |  |

| cc3                            | V <sub>cc</sub> Active Current                                           |        | 50                  | mA             | $\overline{CE} = \overline{OE} = V_{IL}, O_{0-7} = 0,$<br>F = 5 MHz.                                                 |  |

| V <sub>IL</sub>                | Input Low Voltage                                                        | -0.1   | 0.8                 | v              |                                                                                                                      |  |

| VIH                            | Input High Voltage                                                       | 2.0    | V <sub>cc</sub> + 1 | v              |                                                                                                                      |  |

| V <sub>ol</sub>                | Output Low Voltage                                                       |        | 0.45                | V              | l <sub>oL</sub> = 2.1 ma                                                                                             |  |

| V <sub>oh</sub>                | Output High Voltage                                                      | 2.4    |                     | V              | I <sub>он</sub> = -400 µА.                                                                                           |  |

#### NOTES:

1. V<sub>cc</sub> must be appied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

2.  $V_{PP}^{\phi}$  cannot be left floating and should be connected to  $V_{cc}$  during read. 3. 0.1  $\mu$ F ceramic capacitor on  $V_{PP}$  is required during programming only, to suppress voltage transients.

4. Inputs only. Does not include I/O.

5. For I/O only.

# M27C256 E27C256

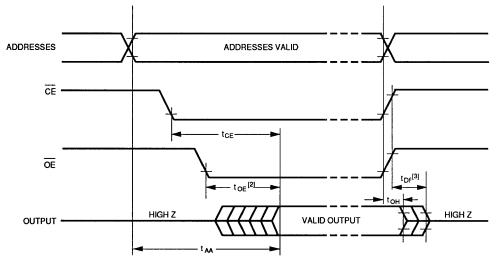

# AC Operating Characteristics During Read

|                                |                                                                                         |      | M27C256-20 M27C256-2<br>E27C256-20 E27C256-2 |      |      |      |      | Test                  |  |

|--------------------------------|-----------------------------------------------------------------------------------------|------|----------------------------------------------|------|------|------|------|-----------------------|--|

| Symbol                         | Parameter                                                                               | Min. | Max.                                         | Min. | Max. | Min. | Max. | Conditions            |  |

| t <sub>AA</sub>                | Address Access Time                                                                     |      | 200                                          |      | 250  |      | 300  | CE=OE=V <sub>IL</sub> |  |

| t <sub>ce</sub>                | Chip Enable to Data Valid                                                               |      | 200                                          |      | 250  |      | 300  | OE=V <sub>IL</sub>    |  |

| t <sub>oe</sub> (2)            | Output Enable to Data Valid                                                             |      | 75                                           |      | 100  |      | 120  | CE=V <sub>IL</sub>    |  |

| t <sub>DF</sub> <sup>(3)</sup> | Output Enable or Chip Enable to Output Float                                            |      | 60                                           |      | 60   |      | 105  | CE=V <sub>1L</sub>    |  |

| t <sub>он</sub>                | Output Hold from Chip Enable,<br>Addresses, or Output Enable<br>whichever occured first | 0    |                                              | 0    |      | 0    |      | CE=OE=V <sub>IL</sub> |  |

## Capacitance<sup>[1]</sup>

| Symbol           | Parameter          | Тур. | Max | Unit | Conditions             |

|------------------|--------------------|------|-----|------|------------------------|

| C                | Input Capacitance  | 4    | 6   | рF   | V <sub>IN</sub> = 0 V  |

| C <sub>out</sub> | Output Capacitance | 8    | 12  | рF   | V <sub>out</sub> = 0 V |

# Equivalent A.C. Test Conditions<sup>[4]</sup>

Output Load: 1 TTL gate and C<sub>L</sub> = 100 pF Input Rise and Fall Times: ≤ 20 ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

# A.C. Waveforms

#### NOTES:

- 1. This parameter is sampled and is not 100% tested.

- 2.  $\overline{OE}$  may be delayed to  $t_{AA} t_{OE}$  after the falling edge of  $\overline{CE}$  without impact on  $t_{AA}$ . 3.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first.

- 4. These are equivalent test conditions and actual test conditions are dependent on the tester.

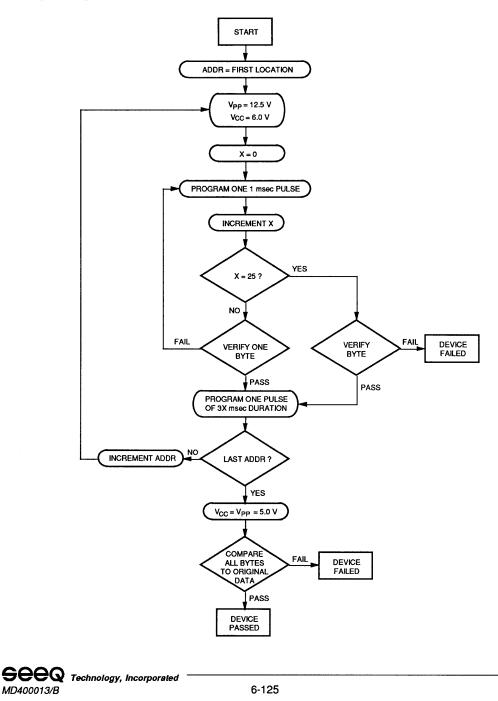

Initially and after erasure, all bits are in the"1" state. An intelligent algorithm is used to program the 27C256 typically in four minutes. Data is programmed using a 12.5V  $V_{PP}$  and an initial chip enable pulse of 1.0 ms.

Incorporated on the 27C256 is Silicon Signature. Silicon Signature contains encoded data which identifies SEEQ as the EPROM manufacturer and gives the product code. This data is encoded in ROM to prevent erasure by ultraviolet light.

#### Erasure Characteristics

The 27C256 is erased using ultraviolet light which has a wavelength of 2537 Angstroms. The integrated dose, i.e., intensity x exposure time, for erasure is a minimum of 15 watt-seconds/cm<sup>2</sup>. The EPROM should be placed within one inch of the lamp tube during erasure. Table 1 shows the typical EPROM erasure time for various light intensities.

#### Table 1. Typical EPROM Erasure Time

| Light Intensity<br>(Micro-Watts/cm²) | Erasure Time<br>(Minutes) |

|--------------------------------------|---------------------------|

| 15,000                               | 20                        |

| 10,000                               | 30                        |

| 5,000                                | 55                        |

#### Silicon Signature

Incorporated in SEEQ's EPROMs is a row of mask programmed read only memory (ROM) cells which is outside of the normal memory cell array. The ROM contains the EPROM's Silicon Signature. Silicon Signature contains data which identifies SEEQ as the manufacturer and gives the product code. This data allows programmers to match the programming specification against the product which is to be programmed. If there is verification, then the programmer proceeds to program.

Silicon Signature is activated by raising address  $A_{0}$  to 12V  $\pm$  0.5V, bringing chip enable and output enable to a TTL low, having all addresses except  $A_{0}$  at a TTL low. The Silicon Signature data is then accessed by toggling  $A_{0}$ . The data appears on outputs  $O_{0}$  to  $O_{0}$ , with  $O_{7}$  used as an odd parity bit (see Table 2).

#### Table 2. Silicon Signature Bytes

|                       | A               | Data (Hex) |

|-----------------------|-----------------|------------|

| SEEQ Code (Byte 0)    | V <sub>IL</sub> | 94         |

| Product Code (Byte 1) | V <sub>IH</sub> | C2         |

#### Programming

The 27C256 is programmed using the industry standard intelligent algorithm.

The intelligent algorithm requires  $V_{cc} = 6$  V and  $V_{PP} = 12.5$  V during byte programming. The initial program pulse width is 1.0 millisecond, followed by a sequence of 1.0 millisecond pulses. A byte is verified after each pulse. A single program pulse, with a time duration equal to 3 times the number of 1.0 millisecond pulses applied, is additionally given to the address after it is verified as being correctly programmed. A minimum of one to a maximum of 25 1-ms pulses, plus one 3X overpulse, may be applied to each byte. When the intelligent algorithm cycle has been completed, all bytes must be read at  $V_{cc} = V_{PP} = 5$  V.

# Intelligent Algorithm Flowchart

M27C256 E27C256

# Intelligent Algorithm

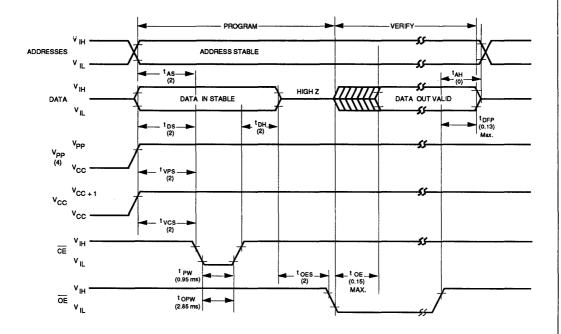

NOTES:

- 1. All times shown in ( ) are minimum and in µsec unless otherwise specified. 2. The input timing reference level is 0.8 V for a  $V_{\mu_i}$  and 2 V for a  $V_{\mu_i}$ . 3.  $t_{o_E}$  and  $t_{o_{FP}}$  are characteristics of the device but must be accomodated by the programmer. 4. 0.1 µF ceramic capacitor on  $V_{p_P}$  is required during programming only, to suppress voltage transients.

# Intelligent Algorithm

# AC Programming Charateristics $T_{A} = 25^{\circ} \pm 5^{\circ}$ C, $V_{cc}$ <sup>[1]</sup> = 6.0 V ± 0.25 V, $V_{pp} = 12.5$ V

| Symbol               | Parameter                           | Min. | Тур. | Max.  | Unit |

|----------------------|-------------------------------------|------|------|-------|------|

| t <sub>AS</sub>      | Address Setup Time                  | 2    |      |       | μs   |

| t <sub>oes</sub>     | OE Setup Time                       | 2    |      |       | μs   |

| t <sub>os</sub>      | Data Setup Time                     | 2    |      |       | μs   |

| t <sub>an</sub>      | Address Hold Time                   | 0    |      |       | μs   |

| t <sub>DH</sub>      | Data Hold Time                      | 2    |      |       | μs   |

| t <sub>dfp</sub>     | Output Enable to Output Float Delay | 0    |      | 130   | ns   |

| t <sub>vps</sub>     | V <sub>PP</sub> Setup Time          | 2    |      |       | μs   |

| t <sub>vcs</sub>     | V <sub>cc</sub> Setup Time          | 2    |      |       | μs   |

| t <sub>PW</sub>      | CE Initial Program Pulse Width      | 0.95 | 1.0  | 1.05  | ms   |

| t <sub>opw</sub> [3] | CE Overprogram Pulse Width          | 2.85 |      | 78.75 | ms   |

| t <sub>oe</sub>      | Data Valid from OE                  |      |      | 150   | ns   |

#### NOTES:

- V<sub>cc</sub> must be applied simultaneously or before V<sub>pp</sub> and removed simultaneously or after V<sub>pp</sub>.

The length of the overprogram pulse will vary from 2.85 msec to 78.75 msec as a function of the iteration counter value X.

# AC Conditions of Test

| Input Rise and Fall Times (10% to 90%) |       | 20 ns      |

|----------------------------------------|-------|------------|

| Input Pulse Levels                     | .0.45 | V to 2.4 V |

| Input Timing Reference Level           | 0.8 V | and 2.0 V  |

| Output Timing Reference Level          | 0.8 V | and 2.0 V  |

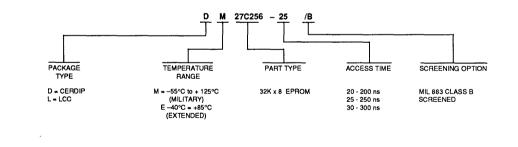

# **Ordering Information**