# MCM68708 MCM68A708

MOS

(N-CHANNEL, SILICON-GATE)

1024 X 8-BIT

**UV ERASABLE PROM**

PIN ASSIGNMENT

L SUFFIX

CERAMIC PACKAGE CASE 716-07

A7

A602

A404 A305

A5 🖸 3

A107

A0**D**8

D1**D**10

D2

VSS**Q**12

A3**D**5 A2**D**6 C SUFFIX

24 VCC

23 **D**A8

22 **D**A9

21 VBB

19 VDD 18 PROGR

17 07

16 DD6

15 DD5

14 DD4

20 DCS/WE

-SEAL CERAMIC PACKAGE CASE 623A-02

#### 1024 X 8 ERASABLE PROM

The MCM68708/68A708 is a 8192-bit Erasable and Electrically Reprogrammable PROM designed for system debug usage and similar applications requiring nonvolatile memory that could be reprogrammed periodically. The transparent window on the package allows the memory content to be erased with ultraviolet light. Pin-for-pin mask-programmable ROMs are available for large volume production runs of systems initially using the MCM68708/68A708.

- Organized as 1024 Bytes of 8 Bits

- Fully Static Operation

- Standard Power Supplies of +12 V, +5 V and -5 V

- Maximum Access Time = 300 ns MCM68A708 450 ns - MCM68708

- Low Power Dissipation

- Chip-Select Input for Memory Expansion

- TTL Compatible

- Three-State Outputs

- Pin Equivalent to the 2708

- Pin-for-Pin Compatible to MCM65308, MCM68308 or 2308 Mask-Programmable ROMs

- Bus Compatible to the M6800 Family

#### PIN CONNECTION DURING READ OR PROGRAM

| Mode    | Pin Number      |                 |                |     |      |     |     |  |  |

|---------|-----------------|-----------------|----------------|-----|------|-----|-----|--|--|

|         | 9-11, 13-17     | 12              | 18             | 19  | 20   | 21  | 24  |  |  |

| Read    | Dout            | ∨ss             | VSS            | VDD | VIL  | V₿₿ | Vcc |  |  |

| Program | D <sub>in</sub> | V <sub>SS</sub> | Pulsed<br>VIHP | VDD | ⊻інw | VBB | Vcc |  |  |

## MCM68708•MCM68A708

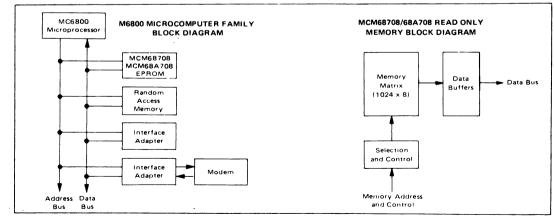

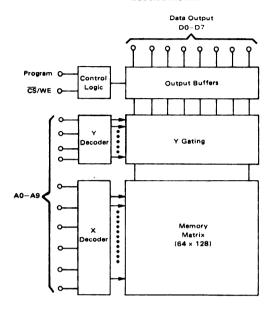

#### BLOCK DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Rating                                                              | Value       | Unit  |

|---------------------------------------------------------------------|-------------|-------|

| Operating Temperature                                               | 0 to +70    | °c    |

| Storage Temperature                                                 | -65 to +125 | °c    |

| VDD with Respect to VBB                                             | +20 to -0.3 | Vdc   |

| V <sub>CC</sub> and V <sub>SS</sub> with Respect to V <sub>BB</sub> | +15 to -0.3 | Vdc   |

| All Input or Output Voltages with<br>Respect to VBB during Read     | +15 to -0.3 | Vdc   |

| CS/WE Input with Respect to VBB<br>during Programming               | +20 to -0.3 | Vdc   |

| Program Input with Respect to VBB                                   | +35 to -0.3 | Vdc   |

| Power Dissipation                                                   | 1.8         | Watts |

#### Note 1:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

# DC READ OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.)

### RECOMMENDED DC READ OPERATING CONDITIONS

| Parameter                |            | Symbol                                                        | Min                  | Nom         | Max                  | Unit     |      |

|--------------------------|------------|---------------------------------------------------------------|----------------------|-------------|----------------------|----------|------|

| Supply Voltage           |            | Vcc                                                           | 4.75                 | 5.0         | 5.25                 | Vdc      |      |

|                          |            |                                                               | VDD                  | 11.4        | 12 .                 | 12.6     | Vdc  |

|                          |            |                                                               | VBB                  | -5.25       | -5.0                 | -4.75    | Vdc  |

| Input High Voltage       |            | VIH                                                           | V <sub>SS</sub> +2.0 | -           | Vcc                  | Vdc      |      |

| Input Low Voltage        |            | VIL                                                           | V <sub>SS</sub> -0.3 | _           | V <sub>SS</sub> +0.8 | Vdc      |      |

| READ OPERATION           | DC CHARAC  | CTERISTICS                                                    |                      | · · · · · · |                      |          |      |

| Characteri               | stic       | Condition                                                     | Symbol               | Min         | Тур                  | Mex      | Unit |

| Address and CS Input Sir | nk Current | V <sub>in</sub> = 5.25 V or V <sub>in</sub> = V <sub>IL</sub> | lin .                | - 1         | 1                    | 10       | μA   |

| Output Leakage Current   |            | V <sub>out</sub> = 5.25 V, CS/WE = 5 V                        | ILO                  | -           | 1                    | 10       | μA   |

| VDD Supply Current       |            | Worst-Case Supply Currents                                    | 1DD                  | 1           | 50                   | 65       | mA   |

| VCC Supply Current       | (Note 2)   | All Inputs High                                               | 1cc                  |             | 6                    | 10       | mA   |

| VBB Supply Current       |            | CS/WE = 5.0 V, T <sub>A</sub> = 0 <sup>0</sup> C              | 188                  | - 1         | 30                   | 45       | mA   |

| Output Low Voltage       | •          | I <sub>OL</sub> = 1.6 mA                                      | VOL                  | - 1         | -                    | VSS +0.4 | v    |

| Output High Voltage      |            | I <sub>OH</sub> = -100 μA                                     | Voн                  | VSS +2.4    | -                    | -        | v    |

| Power Dissipation        | (Note 2)   | T <sub>A</sub> = 70 <sup>o</sup> C                            | PD                   | - 1         | _                    | 800      | mW   |

#### Note 2:

The total power dissipation is specified at 800 mW. It is not calculable by summing the various currents (I<sub>DD</sub>, I<sub>CC</sub>, and I<sub>BB</sub>) multiplied by their respective voltages, since current paths exist between the various power supplies and V<sub>SS</sub>. The I<sub>DD</sub>, I<sub>CC</sub>, and I<sub>BB</sub> currents should be used to determine power supply capacity only.

$v_{BB}$  must be applied prior to  $v_{CC}$  and  $v_{DD}, v_{BB}$  must also be the last power supply switched off.

# MCM68708•MCM68A708

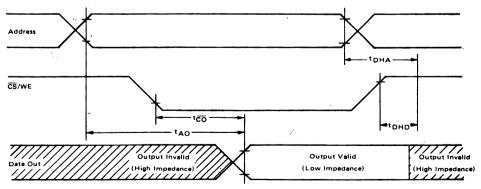

#### AC READ OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.) (All timing with $t_r = t_f = 20 \text{ ns}$ , Load per Note 3)

#### MCM68A708 MCM68708 Max Characteristic Symbol Min Тур Min Тур Max Unit Address to Output Delay 220 300 280 450 ns tAO --Chip Select to Output Delay 60 120 60 120 ns tco \_ \_ Data Hold from Address 10 \_ 10 ns <sup>t</sup>DHA \_ \_ Data Hold from Deselection 10 120 10 120 <sup>t</sup>DHD -ns

#### CAPACITANCE (periodically sampled rather than 100% tested.)

| Characteristic                      | Condition                                                  | Symbol           | Тур | Max | Unit |

|-------------------------------------|------------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance<br>(f = 1.0 MHz)  | V <sub>in</sub> = 0 V, T <sub>A</sub> = 25 <sup>o</sup> C  | C <sub>in</sub>  | 4.0 | 6.0 | ρF   |

| Output Capacitance<br>(f = 1.0 MHz) | V <sub>out</sub> = 0 V, T <sub>A</sub> = 25 <sup>o</sup> C | C <sub>out</sub> | 8.0 | 12  | pF   |

.

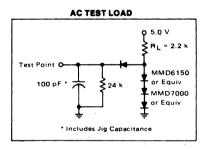

#### Note 3:

Output Load = 1 TTL Gate and  $C_L$  = 100 pF (Includes Jig Capacitance) Timing Measurement Reference Levels: Inputs: 0.8 V and 2.8 V Outputs: 0.8 V and 2.4 V

#### READ OPERATION TIMING DIAGRAM

### DC PROGRAMMING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.)

#### **RECOMMENDED PROGRAMMING OPERATING CONDITIONS**

| Parameter                                     | Symbol | Min   | Nom  | Max                   | Unit |

|-----------------------------------------------|--------|-------|------|-----------------------|------|

| Supply Voltage                                | Vcc    | 4.75  | 5.0  | 5.25                  | Vdc  |

|                                               | VDD    | 11.4  | 12   | 12.6                  | Vdc  |

|                                               | VBB    | -5.25 | -5.0 | -4.75                 | Vdc  |

| Input High Voltage for All Addresses and Data | VIH    | 3.0   | -    | V <sub>CC</sub> + 1.0 | Vdc  |

| Input Low Voltage (except Program)            | VIL    | VSS   | -    | 0.65                  | Vdc  |

| CS/WE Input High Voltage (Note 4)             | VIHW   | 11,4  | 12   | 12.6                  | Vdc  |

| Program Pulse Input High Voltage (Note 4)     | VIHP   | 25    |      | 27                    | Vdc  |

| Program Pulse Input Low Voltage (Note 5)      | VILP   | VSS   | · -  | 1.0                   | Vdc  |

Note 4: Referenced to V<sub>SS</sub>. Note 5: V<sub>IHP</sub> - V<sub>ILP</sub> = 25 V min.

#### **PROGRAMMING OPERATION DC CHARACTERISTICS**

ī.

| Characteristic                       | Condition                         | Symbol          | Min | Тур   | Max | Unit |

|--------------------------------------|-----------------------------------|-----------------|-----|-------|-----|------|

| Address and CS/WE Input Sink Current | V <sub>in</sub> = 5.25 V          | ILI             | -   | -     | 10  | μAdc |

| Program Pulse Source Current         |                                   | IIPL            | -   | - · · | 3.0 | mAdc |

| Program Pulse Sink Current           |                                   | Ірн             | -   | -     | 20  | mAdc |

| VDD Supply Current                   | Worst-Case Supply Currents        | 1DD             | -   | 50    | 65  | mAdc |

| VCC Supply Current                   | All Inputs High                   | Icc             | -   | 6     | 10  | mAdc |

| VBB Supply current                   | CS/WE = 5 V, T <sub>A</sub> = 0°C | I <sub>BB</sub> | -   | 30    | 45  | mAdc |

.

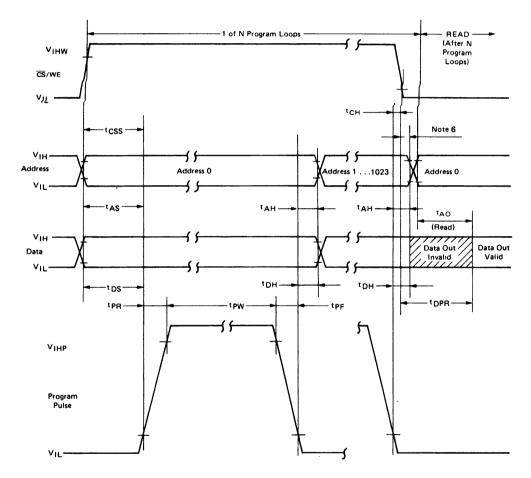

### AC PROGRAMMING OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature unless otherwise noted.)

| Characteristic                      | Symbol          | Min | Max | Unit |

|-------------------------------------|-----------------|-----|-----|------|

| Address Setup Time                  | tAS             | 10  | -   | μs   |

| CS/WE Setup Time                    | tCSS            | 10  | -   | μs   |

| Data Setup Time                     | tDS             | 10  | -   | μs   |

| Address Hold Time                   | <sup>t</sup> AH | 1.0 | -   | μs   |

| CS/WE Hold Time                     | t CH            | 0.5 | -   | μs   |

| Data Hold Time                      | t DH            | 1.0 | -   | μs   |

| Chip Deselect to Ouptut Float Delay | <sup>t</sup> DF | 0   | 120 | ns   |

| Program to Read Delay               | t DPR           | -   | 10  | μs   |

| Program Pulse Width                 | tpw             | 0.1 | 1.0 | ms   |

| Program Pulse Rise Time             | tPR             | 0.5 | 2.0 | μs   |

| Program Pulse Fall Time             | tPF             | 0.5 | 2.0 | μs   |

,

### PROGRAMMING OPERATION TIMING DIAGRAM

Note 6: The CS/WE transistion must occur after the Program Pulse transition and before the Address Transistion.

7

#### **PROGRAMMING INSTRUCTIONS**

After the completion of an ERASE operation, every bit in the device is in the "1" state (represented by Output High). Data are entered by programming zeros (Output Low) into the required bits. The words are addressed the same way as in the READ operation. A programmed "0" can only be changed to a "1" by ultraviolet light erasure.

To set the memory up for programming mode, the  $\overline{CS}$ /WE input (Pin 20) should be raised to +12 V. Programming data is entered in 8-bit words through the data output terminals (D0 to D7).

Logic levels for the data lines and addresses and the supply voltages (V<sub>CC</sub>, V<sub>DD</sub>, V<sub>BB</sub>) are the same as for the READ operation.

After address and data setup one program pulse per address is applied to the program input (Pin 18). A program loop is a full pass through all addresses. Total programming time, Tptotal = N x tpW ≥ 100 ms. The required number of program loops (N) is a function of the program pulse width (tpw), where: 0.1 ms  $\leq$  tpw  $\leq$ 1.0 ms; correspondingly N is:  $100 \le N \le 1000$ . There must be N successive loops through all 1024 addresses. It is not permitted to apply more than one program pulse in succession to the same address (i.e., N program pulses to an address and then change to the next address to be programmed). At the end of a program sequence the  $\overline{CS}/WE$ falling edge transition must occur before the first address transition, when changing from a PROGRAM to a READ cycle. The program pin (Pin 18) should be pulled down to  $V_{ILP}$  with an active device, because this pin sources a small amount of current (IIPL) when CS/WE is at VIHW (12 V) and the program pulse is at V<sub>1LP</sub>.

#### EXAMPLES FOR PROGRAMMING

Always use the  $T_{Ptotal} = N \times t_{PW} \ge 100$  ms relationship.

1. All 8092 bits should be programmed with a 0.2 ms program pulse width.

The minimum number of program loops:

$$N = \frac{1 Ptotal}{t p_W} = \frac{100 ms}{0.2 ms} = 500$$

. One program loop

consists of words 0 to 1023.

- 2. Words 0 to 200 and 300 to 700 are to be programmed. All other bits are "don't care". The program pulse width is 0.5 ms. The minimum number of program loops, N =  $\frac{100}{0.5}$  = 200. One program loop consists of words 0 to 1023. The data entered into the "don't care" bits should be all 1s.

- 3. Same requirements as example 2, but the EPROM is now to be updated to include data for words 850 to 880. The minimum number of program loops is the same as in the previous example, N = 200. One program loop consists of words 0 to 1023. The data entered into the "don't care" bits should be all 1s. Addresses 0 to 200 and 300 to 700 must be reprogrammed with their original data pattern.

#### **ERASING INSTRUCTIONS**

The MCM68708/68A708 can be erased by exposure to high intensity shortwave ultraviolet light, with a wavelength of 2537 Å. The recommended integrated dose (i.e., UV-intensity x exposure time) is 12.5 Ws/cm<sup>2</sup>. As an example, using the "Model 30-000" UV-Eraser (Turner Designs, Mountain View, CA 94043) the ERASE-time is 30 minutes. The lamps should be used without shortwave filters and the MCM68708/68A708 should be positioned about one inch away from the UV-tubes.