The DMA transfer ending conditions vary when channels end individually and when both channels end together.

**Conditions for Channels Ending Individually:** When either of the following conditions are met, the transfer will end in the relevant channel only:

• The value of the channel's DMA transfer count register (TCR) becomes 0.

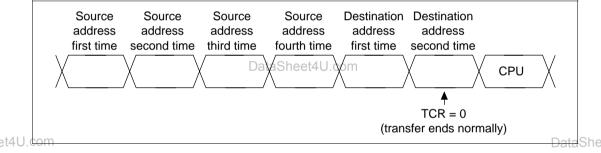

When the TCR value becomes 0, the DMA transfer for that channel ends and the transfer-end flag bit (TE) is set in CHCR. If the IE (interrupt enable) bit has already been set, a DMAC interrupt (DEI) request is sent to the CPU. In 16-byte transfer, when the TCR is 3,2,1 during the final transfer, the source address will be output four times, but the destination address will only be output the number of times found in TCR before transfer ends.

• The DE bit of the DMA channel control register (CHCR) is cleared to 0. When the DMA enable bit (DE) in CHCR is cleared, DMA transfers in the affected channel are halted. The TE bit is not set when this happens.

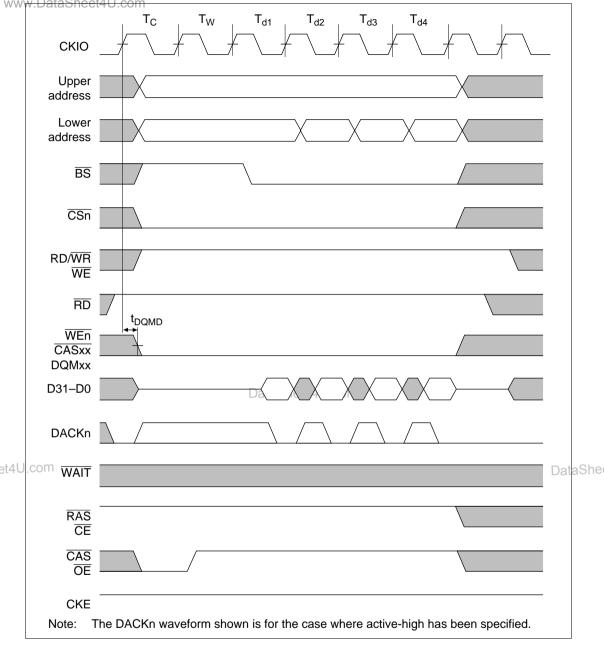

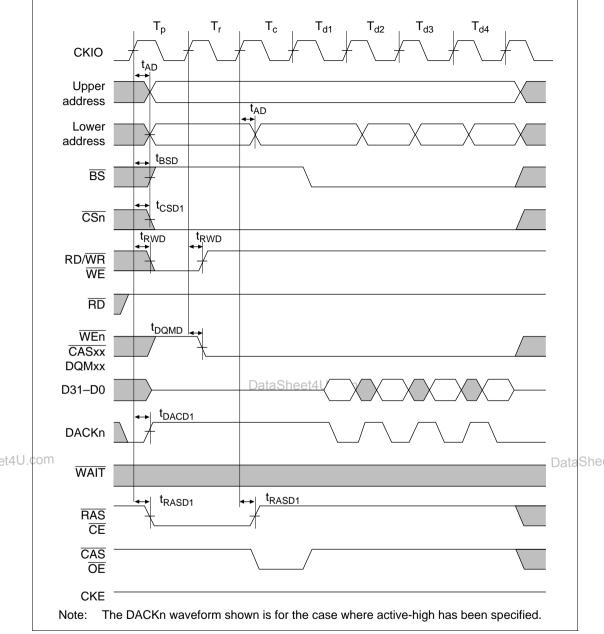

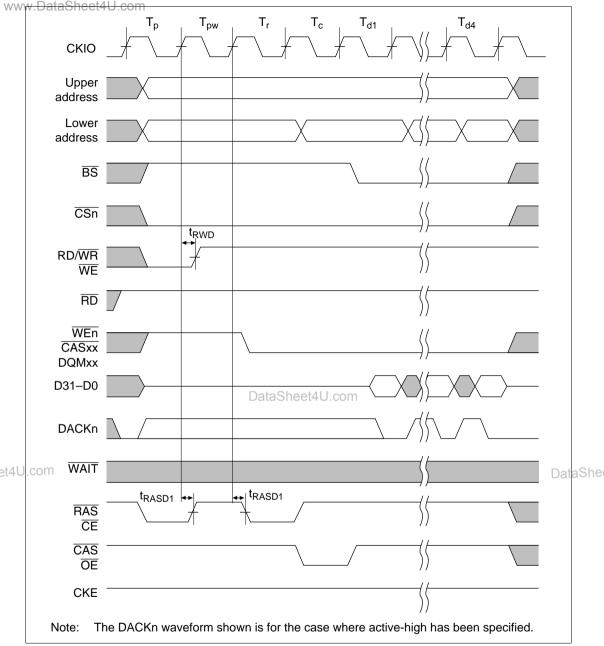

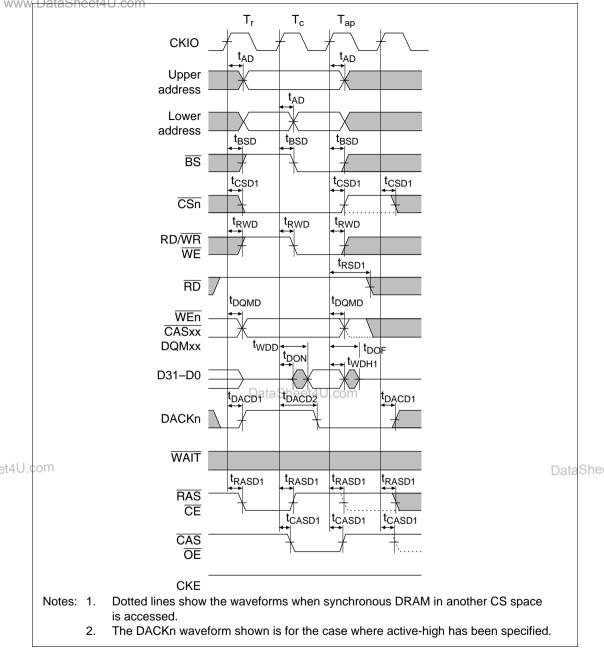

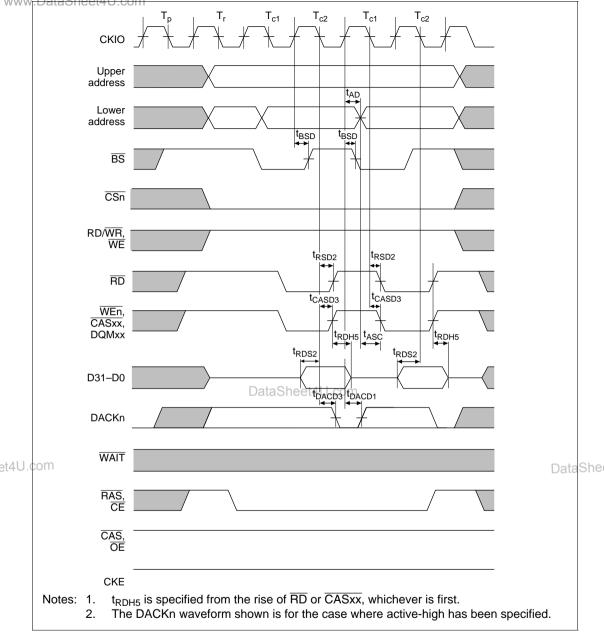

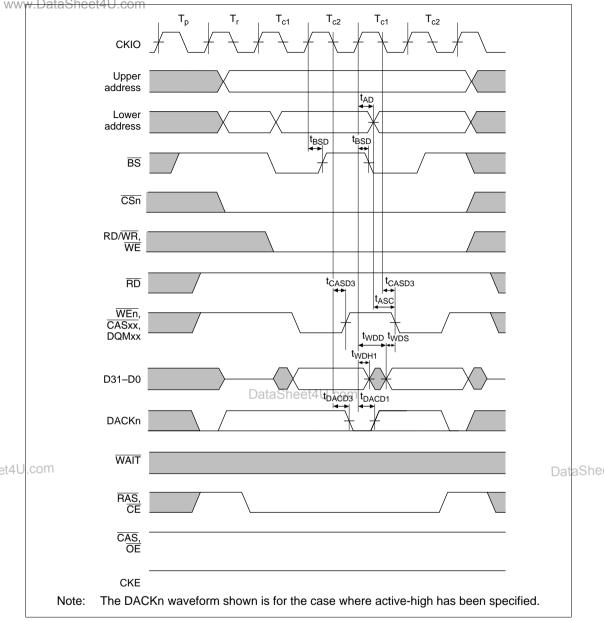

Figure 9.52 16-Byte Transfer when TCR = 2

**Conditions for Both Channels Ending Simultaneously:** Transfers on both channels end when either of the following conditions is met:

• The NMIF (NMI flag) bit or AE (address error flag) bit is set to 1 in DMAOR.

When an NMI interrupt or DMAC address error occurs and the NMIF or AE bit is set to 1 in DMAOR, all channels stop their transfers. The DMA source address register (SAR), designation address register (DAR), and transfer count register (TCR) are all updated by the transfer immediately preceding the halt. When this transfer is the final transfer, TE = 1 and the transfer ends. To resume transfer after NMI interrupt exception handling or address error exception handling, clear the appropriate flag bit. When the DE bit is then set to 1, the transfer on that channel will restart. To avoid this, keep its DE bit at 0. In dual address mode, DMA

DataSheetransfer will be halted after the completion of the following write cycle even when the statessu.com error occurs in the initial read cycle. SAR, DAR and TCR are updated by the final transfer.

www.DataSheet4U.com

• The DMA master enable (DME) bit in DMAOR is cleared to 0.

Clearing the DME bit in DMAOR forcibly aborts the transfers on both channels at the end of the current bus cycle. When the transfer is the final transfer, TE = 1 and the transfer ends.

# 9.4 Examples of Use

# 9.4.1 DMA Transfer Between On-Chip SCI and External Memory

In the following example, data received on the on-chip serial communication interface (SCI) is transferred to external memory using DMAC channel 1. Table 9.9 shows the transfer conditions and register settings.

# Table 9.9 Register Settings for Transfers between On-Chip SCI and External Memory

| Transfer Conditions                                          | Register | Setting             |

|--------------------------------------------------------------|----------|---------------------|

| Transfer source: RDR of on-chip SCI                          | SAR1     | H'FFFFE05           |

| Transfer destination: external memory (word space)           | DAR1     | Destination address |

| Number of transfers: 64                                      | TCR1     | H'0040              |

| Transfer destination address: incremented                    | CHCR1    | H'4045              |

| Transfer source address: fixed                               |          |                     |

| Bus mode: cycle-steal DataSheet4U.com                        |          |                     |

| Transfer unit: byte                                          |          |                     |

| DEI interrupt request generated at end of transfer (DE = 1)  |          |                     |

| Channel priority: Fixed $(0 > 1)$ (DME = 1)                  | DMAOR    | H'0001              |

| Transfer request source (transfer request signal): SCI (RXI) | DRCR1    | H'01 DataS          |

|                                                              |          | ÷.                  |

Note: Check the CPU interrupt level when interrupts are enabled in the SCI.

DataSheet4U.com

www.DataSheet4U.com

- 1. DMA request/response selection control registers 0 and 1 (DRCR0 and DRCR1) should be accessed in bytes. All other registers should be accessed in longword units.

- 2. Before rewriting CHCR0, CHCR1, DRCR0, and DRCR1, first clear the DE bit for the specified channel to 0 or clear the DME bit in DMAOR to 0.

- 3. When the DMAC is not operating, the NMIF bit in DMAOR is set even when an NMI interrupt is input.

- 4. When the cache is used as on-chip RAM, the DMAC cannot access this RAM.

- 5. Set to standby mode after the DME bit in DMAOR is set to 0.

- 6. Do not access the DMAC, BSC, and UBC on-chip peripheral modules.

- 7. Do not access the cache (address array, data array, associative purge area).

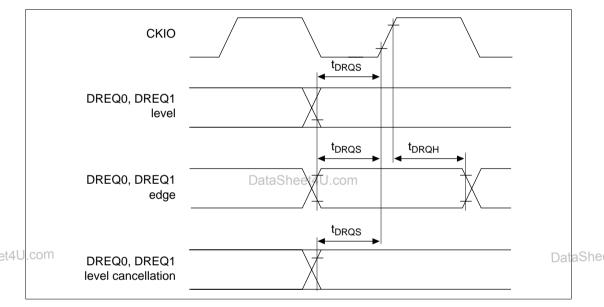

- 8. To detect the DREQ pin signal in single address mode, use edge detection.

DataSheet4U.com

et4U.com

DataShe

DataSheet4U.com

www.DataSheet4U.com

DataSheet4U.com

et4U.com

DataShe

DataSheet4U.com

www.DataSheet4U.com

286 DataSheet4U.com

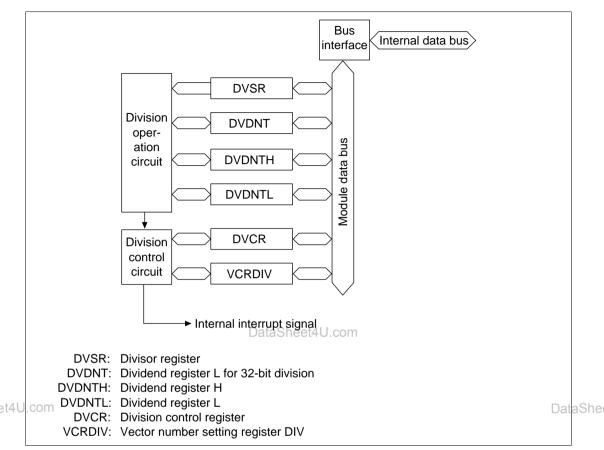

# Section 10 Division Unit

# 10.1 Overview

The division unit (DIVU) divides 64 bits by 32 bits and 32 bits by 32 bits. The results are expressed as a 32-bit quotient and a 32-bit remainder. When the operation produces an overflow, an interrupt can be generated as specified.

# 10.1.1 Features

The division unit has the following features:

- Performs signed division of 64 bits by 32 bits and 32 bits by 32 bits

- Handles 32-bit quotient, 32-bit remainder

- Completes operation execution in 39 cycles

- Controls enabling/disabling of over/underflow interrupts

- Even during the division process, instructions not accessing the division unit can be parallelprocessed

DataSheet4U.com

t4U.com

DataShe

DataSheet4U.com

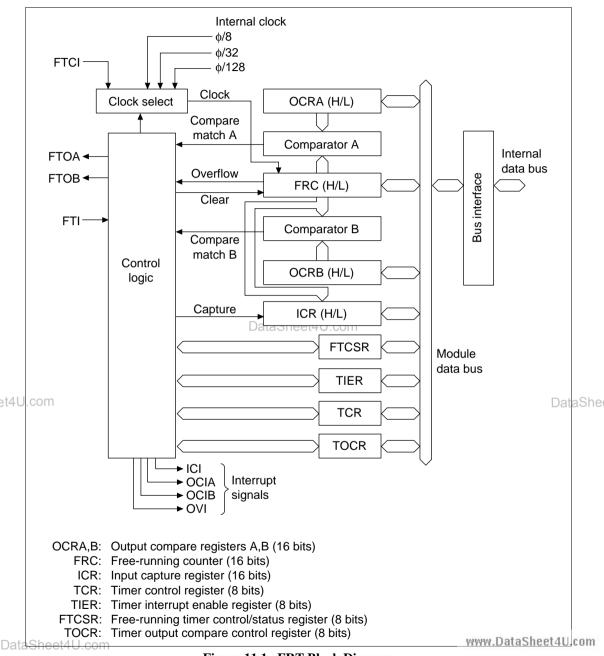

Figure 10.1 shows a block diagram of the division unit.

# 10.1.3 Register Configuration

Table 10.1 shows the register configuration of the division unit.

DataSheet4U.com

www.DataSheet4U.com

288

DataSheet4U.com

### ww.DataSheet4U.com Table 10.1 Division Unit Register Configuration

| Register                                | Abbr.  | R/W | Initial Value           | Address    | Access Size <sup>*1</sup> |

|-----------------------------------------|--------|-----|-------------------------|------------|---------------------------|

| Divisor register                        | DVSR   | R/W | Undefined               | H'FFFFFF00 | 32                        |

| Dividend register L for 32-bit division | DVDNT  | R/W | Undefined               | H'FFFFFF04 | 32                        |

| Division control register               | DVCR   | R/W | H'00000000              | H'FFFFF68  | 16, 32                    |

| Vector number setting register DIV      | VCRDIV | R/W | Undefined <sup>*2</sup> | H'FFFFFF0C | 16, 32                    |

| Dividend register H                     | DVDNTH | R/W | Undefined               | H'FFFFFF10 | 32                        |

| Dividend register L                     | DVDNTL | R/W | Undefined               | H'FFFFFF14 | 32                        |

Notes: 1. Accesses to the division unit are read and written in 32-bit units. DVCR and VCRDIV permit 16 and 32-bit accesses. When registers other than CONT and VCRDIV are accessed with word accesses, undefined values are read or written.

2. The initial value of VCRDIV is H'0000\*\*\*\* (asterisks represent undefined values).

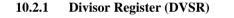

# **10.2** Description of Registers

t4U.com

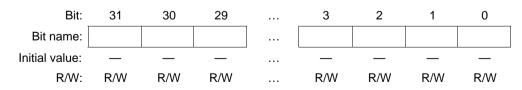

The divisor register (DVSR) is a 32-bit read/write register in which the divisor for the operation is written. It is not initialized by a power-on reset or manual reset, in standby mode, or during module standbys.

# 10.2.2 Dividend Register L for 32-Bit Division (DVDNT)

DataSheet4U.com

www.DataSheet4U.com The dividend register L for 32-bit division (DVDNT) is a 32-bit read/write register in which the 32-bit dividend used for 32-bit ÷ 32-bit division operations is written. When 32-bit ÷ 32-bit division is run, the value set as the dividend is lost and the quotient written at the end of division. When this register is written to, the same value is written in the DVDNTL register. The MSB written is sign-extended in the DVDNTH register. Writing to this register starts the 32-bit  $\div$  32-bit division operation. It is not initialized by a power-on reset or manual reset, in standby mode, or during module standbys.

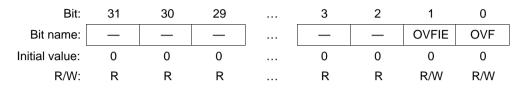

### 10.2.3 **Division Control Register (DVCR)**

The division control register (DVCR) is a 32-bit read/write register, but is also 16-bit accessible. It controls enabling/disabling of the overflow interrupt. This register is initialized to H'00000000 by a power-on reset or manual reset. It is not initialized in standby mode or during module standbys.

- Bits 31 to 2: Reserved. These bits always read 0. The write value should always be 0. •

- Bit 1: OVF Interrupt Enable (OVFIE): Selects enabling or disabling of the OVF interrupt • request (OVFI) upon overflow.

| Bit 1:  | OVFIE                                      | Description                                                 |                 |

|---------|--------------------------------------------|-------------------------------------------------------------|-----------------|

| 0       |                                            | Interrupt request (OVFI) caused by OVF disabled             | (Initial value) |

| t4U.com |                                            | Interrupt request (OVFI) caused by OVF enabled              | DataShe         |

| Note:   | Always set the OVF<br>handling for overflo | TE bit before starting the operation whenever execution ws. | ng interrupt    |

Bit 0: Overflow Flag (OVF). Flag indicating an overflow has occurred.

| Bit 0: OVF | Description              |                 |

|------------|--------------------------|-----------------|

| 0          | No overflow has occurred | (Initial value) |

| 1          | Overflow has occurred    |                 |

DataSheet4U.com

290

www.DataSheet4U.com

DataSheet4U.com

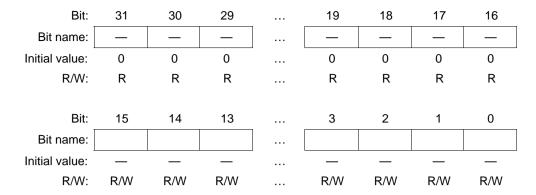

www.DataSheet4U.com 10.2.4 Vector Number Setting Register DIV (VCRDIV)

Vector number setting register DIV (VCRDIV) is a 32-bit read/write register, but is also 16-bit accessible. The destination vector number is set in VCRDIV when an interrupt occurs in the division unit due to an overflow or underflow. Values can be set in the 16 bits from bit 15 to bit 0, but only the last 7 bits (bits 6–0) are valid. Always set 0 for the 9 bits from bit 15 to bit 7. VCRDIV is not initialized by a power-on reset or manual reset, in standby mode, or during module standbys.

- Bits 31 to 7: Reserved. These bits always read 0. The write value should always be 0.

- Bits 6 to 0: Interrupt Vector Number. Sets the interrupt destination vector number. Only the 7 bits 6–0 are valid (as the vector number).

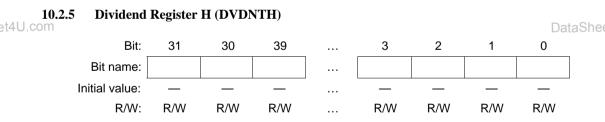

Dividend register H (DVDNTH) is a 32-bit read/write register in which the upper 32 bits of the dividend used for 64 bit ÷ 32 bit division operations are written. When a division operation is executed, the value set as the dividend is lost and the remainder written here at the end of the operation. The initial value of DVDNTH is undefined, and its value is also undefined after a power-on reset or manual reset, in standby mode, and during in module standbys. When the DVDNT register is set with a dividend value, the previous DVDNTH value is lost and the MSB of the DVDNT register is extended to all bits in the DVDNTH register.

DataSheet4U.com

www.DataSheet4U.com

### www.DataSheet4U.com 10.2.6 Dividend Register L (DVDNTL)

Dividend register L (DVDNTL) is a 32-bit read/write register in which the lower 32 bits of the dividend used for 64-bit ÷ 32-bit division operations are written. When a value is set in this register, the 64-bit ÷ 32-bit division operation begins. The value written in the DVDNT register for 32-bit ÷ 32-bit division is also set in this register. When a 64-bit ÷ 32-bit division operation is executed, the value set as the dividend is lost and the quotient written here at the end of the operation. The contents of this register are undefined after a power-on reset or manual reset, in standby mode, and during module standbys.

# 10.3 Operation

# 10.3.1 64-Bit ÷ 32-Bit Operations

64-bit ÷ 32-bit operations work as follows:

- 1. The 32-bit divisor is set in the divisor register (DVSR).

- 2. The 64-bit dividend is set in dividend registers H and L (DVDNTH and DVDNTL). First set the value in DVDNTH. When a value is written to DVDNTL, the 64-bit ÷ 32-bit operation begins.

- DVDNTL). When an overflow occurs, however, the operation ends in 6 cycles. See section 10.3.3, Handling of Overflows, for more information. Note that operation is signed.

- 4. After the operation, the 32-bit remainder is written to DVDNTH and the 32-bit quotient is written to DVDNTL.

# 10.3.2 32-Bit ÷ 32-Bit Operations

32-bit ÷ 32-bit operations work as follows:

- 1. The 32-bit divisor is set in the divisor register (DVSR).

- 2. The 32-bit dividend is set in dividend register L (DVDNT) for 32-bit division. When a value is written to DVDNT, the 32-bit ÷ 32-bit operation begins.

- 3. This unit finishes a single operation in 39 cycles (starting from the setting of the walue is heet 40.com DVDNT). When an overflow occurs, however, the operation ends in 6 cycles. See section

10.3.3, Handling of Overflows, for more information. Note that the operation is signed.

292

www.DataSheet4U.com

4. After the operation, the 32-bit remainder is written to DVDNTH and the 32-bit quotient is written to DVDNT.

#### 10.3.3 Handling of Overflows

When the results of operations exceed the ranges expressed as signed 32 bits (when, in division between two negative numbers, the quotient is the maximum value and a remainder (negative number) is generated) or when the divisor is 0, an overflow will result.

When an overflow occurs, the OVF bit is set and an overflow interrupt is generated if interrupt generation is enabled (the OVFIE bit in DVCR is 1). The operation will then end with the result after 6 cycles of operation stored in the DVDNTH and DVDNTL registers. If interrupt generation is disabled (the OVFIE bit is 0), the operation will end with the operation result at 6 cycles set in DVDNTH and the maximum value H'7FFFFFF or minimum value H'80000000 set in DVDNTL. In the SH7604, the maximum value results when a positive quotient overflows; the minimum value results when a negative quotient overflows. The first three cycles of the 6 cycles executed when an overflow occurs are used for flag setting within the division unit and the next three for division.

### 10.4 **Usage Notes**

#### 10.4.1 Access

All accesses to the division unit except DVCR and VCRDIV must be 32-bit reads or writes. Word accesses to registers other than DVCR and VCRDIV result in reading or writing of undefined values. In the division unit, a read instruction is extended for one cycle immediately after an et4U.comstruction that writes to a register, even if the register is the same, to ensure that the value written taShe is accurately set in the destination register in the division unit.

When a read or write instruction is issued while the division unit is operating, the read or write instruction is continuously extended until the operation ends. This means that instructions that do not access the division unit can be parallel-processed. When an instruction is executed that writes to any register of the division unit immediately following an instruction that writes to the division start-up registers (DVDNTL or DVDNT), the correct value may not be set in the start-up register. Specify an instruction other than one that writes to a division unit register for the instruction immediately following instruction that writes to a start-up register.

Because of the above restrictions, efficient processing can be achieved by executing instructions that do not access the division unit for 39 cycles after starting the operation, then issuing a read instruction after the 39th cycle.

www.DataSheet4U.com

### www.DataSheet4U.com 10.4.2 Overflow Flag

When an overflow occurs, the overflow flag (OVF) is set and is not automatically reset. When OVF is set, the operation is not affected. When necessary, clear it before the operation. The states of registers when overflow occurs are shown in table 10.2.

| Register | Overflow Interrupt Enabled                                                | Overflow Interrupt Disabled                                                                                       |

|----------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| DVSR     | Holds the value written                                                   | Holds the value written                                                                                           |

| DVDNT    | Holds the results of operations until overflow generation is detected*    | The maximum value is set for overflow to<br>the plus side, or the minimum value for<br>overflow to the minus side |

| DVCR     | The OVF bit is set                                                        | The OVF bit is set                                                                                                |

| VCRDIV   | Holds the value written                                                   | Holds the value written                                                                                           |

| DVDNTH   | Holds the results of operations until<br>overflow generation is detected* | Holds the results of operations until<br>overflow generation is detected *                                        |

| DVDNTL   | Holds the results of operations until overflow generation is detected*    | The maximum value is set for overflow to<br>the plus side, or the minimum value for<br>overflow to the minus side |

# Table 10.2 Overflow Processing

Note: In division processing, the intermediate operation result is written for cycles up to detection of overflow generation.

DataSheet4U.com

t4U.com

DataShe

DataSheet4U.com

www.DataSheet4U.com

294 DataSheet4U.com

# Section 11 16-Bit Free-Running Timer

# 11.1 Overview

The SH7604 has a single-channel, 16-bit free-running timer (FRT) on-chip. The FRT is based on a 16-bit free-running counter (FRC) and can output two types of independent waveforms. The FRT can also measure the width of input pulses and the cycle of external clocks.

# 11.1.1 Features

The FRT has the following features:

- Allows selection between four types of counter input clocks. Select from external clock or three types of internal clocks ( $\phi/8$ ,  $\phi/32$ , and  $\phi/128$ ). (External events can be counted.)

- Two independent comparators. Two types of waveforms can be output.

- Input capture. Select rising edge or falling edge.

- Counter clear can be specified. The counter value can be cleared upon compare match A.

- Four types of interrupt sources. Two compare matches, one input capture, and one overflow are available as interrupt sources, and interrupts can be requested independently for each.

DataSheet4U.com

et4U.com

DataShe

DataSheet4U.com

Figure 11.1 shows a block diagram of the FRT.

296

Table 11.1 lists FRT I/O pins and their functions.

# Table 11.1Pin Configuration

| Channel                     | Pin  | I/O | Function                        |

|-----------------------------|------|-----|---------------------------------|

| Counter clock input pin     | FTCI | I   | FRC counter clock input pin     |

| Output compare A output pin | FTOA | 0   | Output pin for output compare A |

| Output compare B output pin | FTOB | 0   | Output pin for output compare B |

| Input capture input pin     | FTI  | I   | Input pin for input capture     |

# 11.1.4 Register Configuration

Table 11.2 shows the FRT register configuration.

# Table 11.2 Register Configuration

| Register                                   | Abbreviation                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                | Initial<br>Value                                                                                                                                                                                                                                                                                                                                                                         | Address                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer interrupt enable register            | TIER                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'01                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE10                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Free-running timer control/status register | tFSCSRt4U.com                                                                                                                                                                                                                                                                                                                                                | R/(W)*1                                                                                                                                                                                                                                                                                                                                                                            | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE11                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Free-running counter H                     | FRC H                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE12                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Free-running counter L                     | FRC L                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE13                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output compare register A H                | OCRA H                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'FF                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFE14*2                                                                                                                                                                                                                                                                                                                                                                                                                                     | Cho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Output compare register A L                | OCRA L                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'FF                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE15*2 Data                                                                                                                                                                                                                                                                                                                                                                                                                               | 1311e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Output compare register B H                | OCRB H                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'FF                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE14* <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output compare register B L                | OCRB L                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'FF                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE15* <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timer control register                     | TCR                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE16                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timer output compare control register      | TOCR                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                | H'E0                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE17                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input capture register H                   | ICR H                                                                                                                                                                                                                                                                                                                                                        | R                                                                                                                                                                                                                                                                                                                                                                                  | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE18                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input capture register L                   | ICR L                                                                                                                                                                                                                                                                                                                                                        | R                                                                                                                                                                                                                                                                                                                                                                                  | H'00                                                                                                                                                                                                                                                                                                                                                                                     | HFFFFFE19                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                            | Timer interrupt enable register<br>Free-running timer control/status register<br>Free-running counter H<br>Free-running counter L<br>Output compare register A H<br>Output compare register A L<br>Output compare register B H<br>Output compare register B L<br>Timer control register<br>Timer output compare control register<br>Input capture register H | Timer interrupt enable registerTIERFree-running timer control/status registerFTCSRI4U.comFree-running counter HFRC HFree-running counter LFRC LOutput compare register A HOCRA HOutput compare register A LOCRA LOutput compare register B HOCRB HOutput compare register B LOCRB LTimer control registerTCRTimer output compare control registerTOCRInput capture register HICR H | Timer interrupt enable registerTIERR/WFree-running timer control/status register FTCSR!4U.comR/(W)*1Free-running counter HFRC HR/WFree-running counter LFRC LR/WOutput compare register A HOCRA HR/WOutput compare register A LOCRA LR/WOutput compare register B HOCRB HR/WOutput compare register B LOCRB LR/WTimer control registerTCRR/WTimer output compare control registerTOCRR/W | RegisterAbbreviationR/WValueTimer interrupt enable registerTIERR/WH'01Free-running timer control/status register FTCSRI4U.comR/(W)*1H'00Free-running counter HFRC HR/WH'00Free-running counter LFRC LR/WH'00Output compare register A HOCRA HR/WH'FFOutput compare register A LOCRA LR/WH'FFOutput compare register B HOCRB HR/WH'FFOutput compare register B LOCRB LR/WH'FFTimer control registerTCRR/WH'E0Input capture register HICR HRH'00 | RegisterAbbreviationR/WValueAddressTimer interrupt enable registerTIERR/WH'01HFFFFE10Free-running timer control/status register FTCSRt4U.comR/(W)*1H'00HFFFFE11Free-running counter HFRC HR/WH'00HFFFFE12Free-running counter LFRC LR/WH'00HFFFFE13Output compare register A HOCRA HR/WH'FFHFFFFE15*2Output compare register A LOCRA LR/WH'FFHFFFFE15*2Output compare register B HOCRB HR/WH'FFHFFFFE15*2Output compare register B LOCRB LR/WH'FFHFFFFE15*2Timer control registerTCRR/WH'G0HFFFFE16Timer output compare control registerTOCRR/WH'E0HFFFFE17Input capture register HICR HRH'00HFFFFE18 |

Notes: 1. Bits 7 to 1 are read-only. The only value that can be written is a 0, which is used to clear flags. Bit 0 can be read or written.

- 2. OCRA and OCRB have the same address. The OCRS bit in TOCR is used to switch between them.

- 3. Use byte-size access for all registers.

DataSheet4U.com

www.DataSheet4U.com

# www.DataSheet4U.com 11.2 Register Descriptions

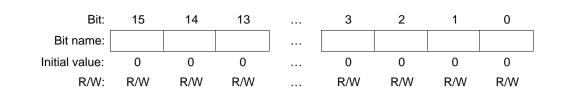

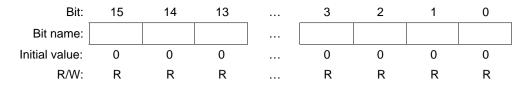

**Free-Running Counter (FRC)**

11.2.1

FRC is a 16-bit read/write up-counter. It increments upon input of a clock. The input clock can be selected using clock select bits 1 and 0 (CKS1, CKS0) in TCR. FRC can be cleared upon compare match A.

When FRC overflows (H'FFFF  $\rightarrow$  H'0000), the overflow flag (OVF) in FTCSR is set to 1. FRC can be read or written to by the CPU, but because it is 16 bits long, data transfers involving the CPU are performed via a temporary register (TEMP). See section 11.3, CPU Interface, for more detailed information.

FRC is initialized to H'0000 by a reset, in standby mode, and when the module standby function is used.

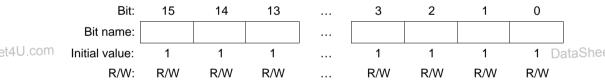

# 11.2.2 Output Compare Registers A and B (OCRA and OCRB)

OCR is composed of two 16-bit read/write registers (OCRA and OCRB). The contents of OCR are always compared to the FRC value. When the two values are the same, the output compare flags in FTCSR (OCFA and OCFB) are set to 1.

When the OCR and FRC values are the same (compare match), the output level values set in the output level bits (OLVLA and OLVLB) are output to the output compare pins (FTOA and FTOB). After a reset, FTOA and FTOB output 0 until the first compare match occurs.

Because OCR is a 16-bit register, data transfers involving the CPU are performed via a temporary register (TEMP). See section 11.3, CPU Interface, for more detailed information.

Data SOCR is initialized to H'FFFF by a reset, in standby mode, and when the module standby matching 4U.com is used.

# DataSheet4U.com

298

www.DataSheet4U.com

Input Capture Register (ICR) 11.2.3

ICR is a 16-bit read-only register. When a rising edge or falling edge of the input capture signal is detected, the current FRC value is transferred to ICR. At the same time, the input capture flag (ICF) in FTCSR is set to 1. The edge of the input signal can be selected using the input edge select bit (IEDGA) in TCR.

Because ICR is a 16-bit register, data transfers involving the CPU are performed via a temporary register (TEMP). See Section 11.3, CPU Interface, for more detailed information. To ensure that the input capture operation is reliably performed, set the pulse width of the input capture input signal to six system clocks ( $\phi$ ) or more.

ICR is initialized to H'0000 by a reset, in standby mode, and when the module standby function is used.

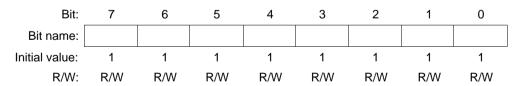

| 11.2.  | 11.2.4 Timer Interrupt Enable Register (TIER) |      |   |               |               |       |       |      |         |

|--------|-----------------------------------------------|------|---|---------------|---------------|-------|-------|------|---------|

|        | Bit:                                          | 7    | 6 | DataShee<br>5 | et4U.com<br>4 | 3     | 2     | 1    | 0       |

|        | Bit name:                                     | ICIE | — | —             | —             | OCIAE | OCIBE | OVIE | —       |

|        | Initial value:                                | 0    | 0 | 0             | 0             | 0     | 0     | 0    | 1       |

| 4U com | R/W:                                          | R/W  | _ | _             | _             | R/W   | R/W   | R/W  | -DataSh |

TIER is an 8-bit read/write register that controls enabling of all interrupt requests. TIER is initialized to H'01 by a reset, in standby mode, and when the module standby function is used.

Bit 7-Input Capture Interrupt Enable (ICIE): Selects enabling/disabling of the ICI interrupt • request when the input capture flag (ICF) in FTCSR is set to 1.

| Bit 7: ICIE | Description                                    |                 |

|-------------|------------------------------------------------|-----------------|

| 0           | Interrupt request (ICI) caused by ICF disabled | (Initial value) |

| 1           | Interrupt request (ICI) caused by ICF enabled  |                 |

Bits 6 to 4—Reserved: These bits always read 0. The write value should always be 0. Do not DataSheet4U.com www.DataSheet4U.com

# Renesas

www.DataSheet4U.com

Bit 3—Output Compare Interrupt A Enable (OCIAE): Selects enabling/disabling of the OCIA interrupt request when the output compare flag A (OCFA) in FTCSR is set to 1.

| Bit 3: OCIAE | Description                                      |                 |

|--------------|--------------------------------------------------|-----------------|

| 0            | Interrupt request (OCIA) caused by OCFA disabled | (Initial value) |

| 1            | Interrupt request (OCIA) caused by OCFA enabled  |                 |

Bit 2—Output Compare Interrupt B Enable (OCIBE): Selects enabling/disabling of the OCIB interrupt request when the output compare flag B (OCFB) in FTCSR is set to 1.

| Bit 2: OCIBE | Description                                      |                 |

|--------------|--------------------------------------------------|-----------------|

| 0            | Interrupt request (OCIB) caused by OCFB disabled | (Initial value) |

| 1            | Interrupt request (OCIB) caused by OCFB enabled  |                 |

Bit 1—Timer Overflow Interrupt Enable (OVIE): Selects enabling/disabling of the OVI interrupt request when the overflow flag (OVF) in FTCSR is set to 1.

| Bit 1: OVIE | Description                                     |                 |

|-------------|-------------------------------------------------|-----------------|

| 0           | Interrupt request (FOVI) caused by OVF disabled | (initial value) |

| 1           | Interrupt request (FOVI) caused by OVF enabled  |                 |

Bit 0—Reserved: This bit always reads 1. The write value should always be 1.

### 11.2.5 Free-Running Timer Control/Status Register (FTCSR)

et4U.com

| Bit:           | 7      | 6 | 5 | 4 | 3      | 2      | 1      | 0     | laono |

|----------------|--------|---|---|---|--------|--------|--------|-------|-------|

| Bit name:      | ICF    | — | — | — | OCFA   | OCFB   | OVF    | CCLRA |       |

| Initial value: | 0      | 0 | 0 | 0 | 0      | 0      | 0      | 0     |       |

| R/W:           | R/(W)* | _ | _ | _ | R/(W)* | R/(W)* | R/(W)* | R/W   |       |

Note: For bits 7, and 3 to 1, the only value that can be written is 0 (to clear the flags).

FTCSR is an 8-bit register that selects counter clearing and controls interrupt request signals. FTCSR is initialized to H'00 by a reset, in standby mode, and when the module standby function is used. See section 11.4, Operation, for the timing.

Bit 7—Input Capture Flag (ICF): Status flag that indicates that the FRC value has been sent to FICR by the input capture signal. This flag is cleared by software and set by hardware. It cannot be set by software.

### www.DataSheet4U.com

| WWW. | DataSheet4U.com<br>Bit 7: ICF | Description                                                            |                              |

|------|-------------------------------|------------------------------------------------------------------------|------------------------------|

|      | 0                             | Clear conditions: When ICF is read while set to 1, and t written to it | then 0 is<br>(Initial value) |

|      | 1                             | Set conditions: When the FRC value is sent to ICR by t capture signal  | he input                     |

- Bits 6 to 4—Reserved: These bits always read 0. The write value should always be 0.

- Bit 3—Output Compare Flag A (OCFA): Status flag that indicates when the values of the FRC and OCRA match. This flag is cleared by software and set by hardware. It cannot be set by software.

| Bit 3: OCFA | Description                                                                                     |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------|--|--|--|

| 0           | Clear conditions: When OCFA is read while set to 1, and then 0 is written to it (Initial value) |  |  |  |

| 1           | Set conditions: When the FRC value becomes equal to OCRA                                        |  |  |  |

• Bit 2—Output Compare Flag B (OCFB): Status flag that indicates when the values of FRC and OCRB match. This flag is cleared by software and set by hardware. It cannot be set by software.

| Bit 2: OCFB | Description<br>DataSheet4U.com                            |                                              |

|-------------|-----------------------------------------------------------|----------------------------------------------|

| 0           | Clear conditions: When OCFB is read whil<br>written to it | e set to 1, and then 0 is<br>(Initial value) |

| 1           | Set conditions: When the FRC value beco                   | mes equal to OCRB                            |

t4U.com

• Bit 1—Timer Overflow Flag (OVF): Status flag that indicates when FRC overflows (from H'FFFF to H'0000). This flag is cleared by software and set by hardware. It cannot be set by software.

| Bit 1: OVF | Description                                                                           |                |

|------------|---------------------------------------------------------------------------------------|----------------|

| 0          | Clear conditions: When OVF is read while set to 1, and then 0 i written to it (Initia | is<br>I value) |

| 1          | Set conditions: When the FRC value changes from H'FFFF to H                           | H'0000         |

• Bit 0—Counter Clear A (CCLRA): Selects whether or not to clear FRC on compare match A (signal indicating match of FRC and OCRA).

DataSheet4U.com

www.DataSheet4U.com

| WWW | /.DataSheet4U.com<br>Bit 0: CCLRA | Description                    |                 |

|-----|-----------------------------------|--------------------------------|-----------------|

|     | 0                                 | FRC clear disabled             | (Initial value) |

|     | 1                                 | FRC cleared on compare match A |                 |

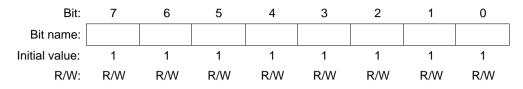

## 11.2.6 Timer Control Register (TCR)

| Bit:           | 7     | 6   | 5   | 4   | 3   | 2   | 1    | 0    |

|----------------|-------|-----|-----|-----|-----|-----|------|------|

| Bit name:      | IEDGA | —   | —   |     | —   | —   | CKS1 | CKS0 |

| Initial value: | 0     | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

| R/W:           | R/W   | R/W | R/W | R/W | R/W | R/W | R/W  | R/W  |

TCR is an 8-bit read/write register that selects the input edge for input capture and selects the input clock for FRC. TCR is initialized to H'00 by a reset, in standby mode, and when the module standby function is used.

• Bit 7—Input Edge Select (IEDG): Selects whether to capture the input capture input (FTI) on the falling edge or rising edge.

| Bit 7: IEDG | Description                     |                 |

|-------------|---------------------------------|-----------------|

| 0           | Input captured on falling edge  | (Initial value) |

| 1           | Input captured on rising edgeom |                 |

Bits 6 to 2—Reserved: These bits always read 0. The write value should always be 0. Do not write 1.

Com

et4U.com

• Bits 1 and 0—Clock Select (CKS1, CKS0): These bits select whether to use an external clock or one of three internal clocks for input to FRC. The external clock is counted at the rising edge.

| Bit 1: CKS1 | Bit 0: CKS0 | Description                          |                 |

|-------------|-------------|--------------------------------------|-----------------|

| 0           | 0           | Internal clock: count at \$\phi/8    | (Initial value) |

|             | 1           | Internal clock: count at \$/32       |                 |

| 1           | 0           | Internal clock: count at $\phi/128$  |                 |

|             | 1           | External clock: count at rising edge |                 |

DataSheet4U.com

302

www.DataSheet4U.com

DataSheet4U.com

### www.DataSheet4U.com

# 11.2.7 Timer Output Compare Control Register (TOCR)

| Bit:           | 7 | 6 | 5 | 4    | 3   | 2   | 1     | 0     |

|----------------|---|---|---|------|-----|-----|-------|-------|

| Bit name:      |   | _ | — | OCRS | —   |     | OLVLA | OLVLB |

| Initial value: | 1 | 1 | 1 | 0    | 0   | 0   | 0     | 0     |

| R/W:           | _ | _ | _ | R/W  | R/W | R/W | R/W   | R/W   |

TOCR is an 8-bit read/write register that selects the output level for output compare, enables output compare output, and controls switching between access of output compare registers A and B. TOCR is initialized to H'E0 by a reset, in standby mode, and when the module standby function is used.

Bits 7 to 5—Reserved: These bits always read 1. The write value should always be 1. Do not write 0.

Bit 4—Output Compare Register Select (OCRS): OCRA and OCRB share the same address. The OCRS bit controls which register is selected when reading/writing to this address. It does not affect the operation of OCRA and OCRB.

| Bit 4: OCRS | Description                  |                 |

|-------------|------------------------------|-----------------|

| 0           | OCRA register selected       | (Initial value) |

| 1           | OCRB register selected U.com |                 |

Bits 3 and 2—Reserved: These bits always read 0. The write value should always be 0. Do not write 1.

# et4U.com

Bit 1—Output Level A (OLVLA): Selects the level output to the output compare A output pin DataShee upon compare match A (signal indicating match of FRC and OCRA).

| Bit 1: OLVLA | Description                 |                 |

|--------------|-----------------------------|-----------------|

| 0            | 0 output on compare match A | (Initial value) |

| 1            | 1 output on compare match A |                 |

Bit 0—Output Level B (OLVLB): Selects the level output to the output compare B output pin upon compare match B (signal indicating match of FRC and OCRB).

| Description                 |                             |

|-----------------------------|-----------------------------|

| 0 output on compare match B | (Initial value)             |

| 1 output on compare match B | www.DataSheet4U.com         |

|                             | 0 output on compare match B |

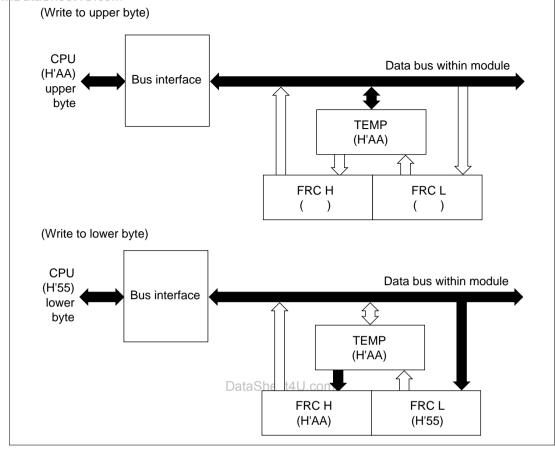

FRC, OCRA, OCRB, and FICR are 16-bit registers. The data bus width between the CPU and FRT, however, is only 8 bits. Access of these three types of registers from the CPU therefore needs to be performed via an 8-bit temporary register called TEMP.

The following describes how these registers are read from and written to:

• Writing to 16-bit Registers

The upper byte is written, which results in the upper byte of data being stored in TEMP. The lower byte is then written, which results in 16 bits of data being written to the register when combined with the upper byte value in TEMP.

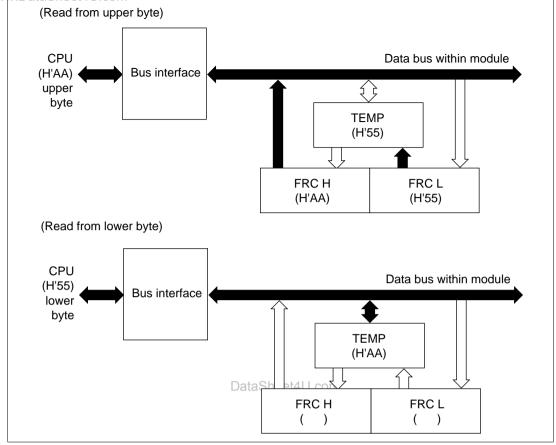

• Reading from 16-bit Registers

The upper byte of data is read, which results in the upper byte value being transferred to the CPU. The lower byte value is transferred to TEMP. The lower byte is then read, which results in the lower byte value in TEMP being sent to the CPU.

When registers of these three types are accessed, two byte accesses should always be performed, first to the upper byte, then the lower byte. The same applies to accesses with the on-chip direct memory access controller. If only the upper byte or lower byte is accessed, the data will not be transferred properly.

Figure 11.2 and 11.3 show the flow of data when FRC is accessed. Other registers function in the same way. When reading OCRA and OCRB, however, both upper and lower-byte data is transferred directly to the CPU without passing through TEMP.

t4U.com

DataShe

DataSheet4U.com

www.DataSheet4U.com

www.DataSheet4U.com

et4U.com

Figure 11.2 FRC Access Operation (CPU Writes H'AA55 to FRC)

DataSheet4U.com

www.DataSheet4U.com

RENESAS

DataShe

et4U.com

Figure 11.3 FRC Access Operation (CPU Reads H'AA55 from FRC)

DataShe

DataSheet4U.com

www.DataSheet4U.com

306 DataSheet4U.com

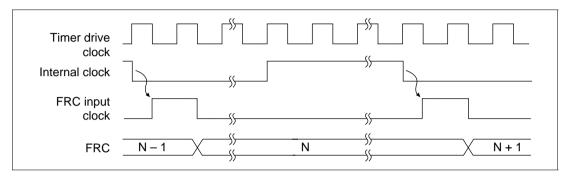

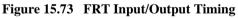

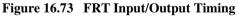

# 11.4.1 FRC Count Timing

The FRC increments on clock input (internal or external).

**Internal Clock Operation:** Set the CKS1 and CKS0 bits in TCR to select which of the three internal clocks created by dividing system clock  $\phi$  ( $\phi/8$ ,  $\phi/32$ ,  $\phi/128$ ) is used. Figure 11.4 shows the timing.

Figure 11.4 Count Timing (Internal Clock Operation)

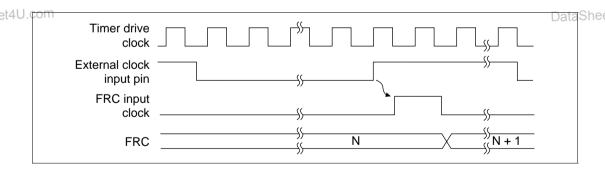

**External Clock Operation:** Set the CKS1 and CKS0 bits in TCR to select the external clock. External clock pulses are counted on the rising edge. The pulse width of the external clock must be at least 6 system clocks ( $\phi$ ). A smaller pulse width will result in inaccurate operation. Figures 11.5 shows the timing.

Figure 11.5 Count Timing (External Clock Operation)

DataSheet4U.com

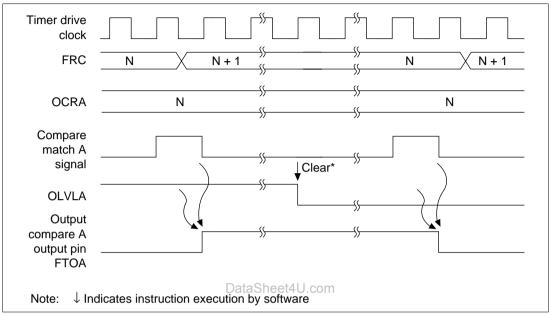

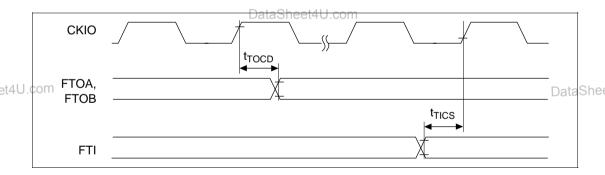

When a compare match occurs, the output level set in the OLVL bit in TOCR is output from the output compare output pins (FTOA, FTOB). Figure 11.6 shows the timing for output of output compare A.

Figure 11.6 Output Timing for Output Compare A

# et4U.011.4.3 FRC Clear Timing

DataShe

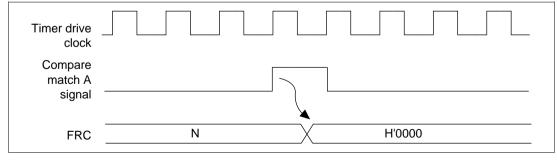

FRC can be cleared on compare match A. Figure 11.7 shows the timing.

Figure 11.7 Compare Match A Clear Timing

DataSheet4U.com

www.DataSheet4U.com

# 308

DataSheet4U.com

# 11.4.4 Input Capture Input Timing

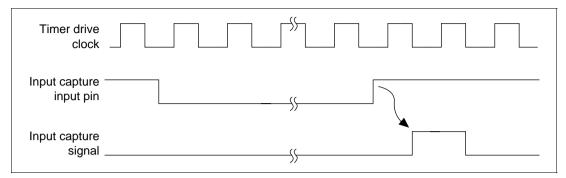

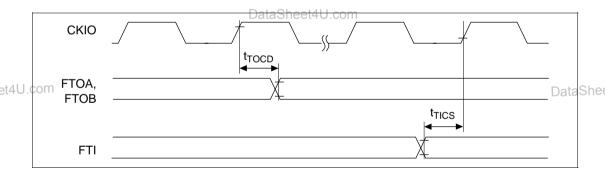

Either the rising edge or falling edge, can be selected for input capture input using the IEDG bit in TCR. Figure 11.8 shows the timing when the rising edge is selected (IEDG = 1).

Figure 11.8 Input Capture Signal Timing (Normal)

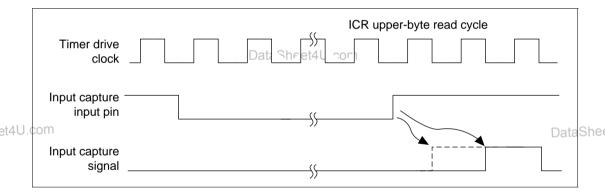

When the input capture signal is input when ICR is read (upper-byte read), the input capture signal is delayed by one cycle of the clock that drives the timer. Figure 11.9 shows the timing.

Figure 11.9 Input Capture Signal Timing (Input Capture Input when ICR is Read)

DataSheet4U.com

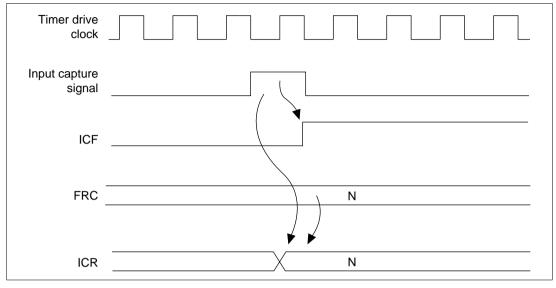

Input capture input sets the input capture flag (ICF) to 1 and simultaneously transfers the FRC value to ICR. Figure 11.10 shows the timing.

Figure 11.10 ICF Setting Timing DataSheet4U.com

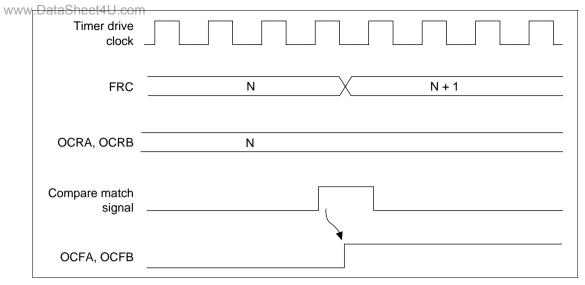

# 11.4.6 Output Compare Flag (OCFA, OCFB) Setting Timing

The compare match signal output (when OCRA or OCRB matches the FRC value) sets output compare flag OCFA or OCFB to 1. The compare match signal is generated in the last state in DataShe which the values matched (at the timing for updating the count value that matched the FRC). After OCRA or OCRB matches the FRC, no compare match signal is generated until the increment lock is generated. Figure 11.11 shows the timing for setting OCFA and OCFB.

DataSheet4U.com

www.DataSheet4U.com

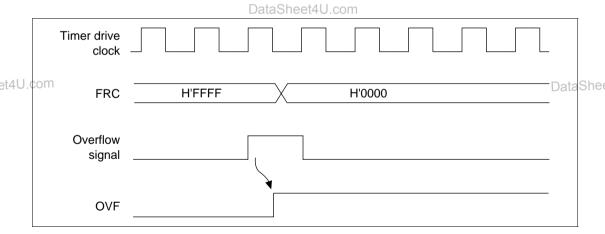

# 11.4.7 Timer Overflow Flag (OVF) Setting Timing

FRC overflow (from H'FFFF to H'0000) sets the timer overflow flag (OVF) to 1. Figure 11.12 shows the timing.

DataSheet4U.com

# www.DataSheet4U.com 11.5 Interrupt Sources

There are four FRT interrupt sources of three types (ICI, OCIA/OCIB, and OVI). Table 11.3 lists the interrupt sources and their priorities after a reset is cleared. The interrupt enable bits in TIER are used to enable or disable the interrupt bits. Each interrupt request is sent to the interrupt controller independently. See section 4, Exception Handling, for more information about priorities and the relationship to interrupts other than those of the FRT.

| Table 11.3 F | <b>FRT Interrupt Sources and Priorities</b> |

|--------------|---------------------------------------------|

|--------------|---------------------------------------------|

| Interrupt Source | Description               | Priority   |

|------------------|---------------------------|------------|

| ICI              | Interrupt by ICF          | High       |

| OCIA, OCIB       | Interrupt by OCFA or OCFB | $\uparrow$ |

| OVI              | Interrupt by OVF          | Low        |

# **11.6 Example of FRT Use**

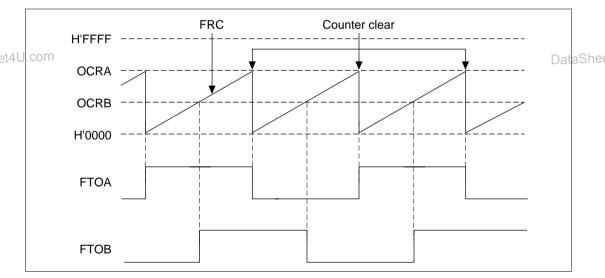

Figure 11.13 shows an example in which pulses with a 50% duty factor and arbitrary phase relationship are output. The procedure is as follows:

- 1. Set the CCLRA bit in FTCSR to 1.

- 2. The OLVLA and OLVLB bits are inverted by software whenever a compare match occurs.

Figure 11.13 Example of Pulse Output

DataSheet4U.com

www.DataSheet4U.com

# 312 DataSheet4U.com

Note that the following contention and operations occur when the FRT is operating:

- 1. FRC operates on the timer drive clock ( $\phi/4$ ), which has a cycle of 4 times the system clock ( $\phi$ ). For this reason, when the CPU performs an access, both the CPU and FRT will be operating, so a WAIT request will be generated from the FRT to the CPU. The number of access cycles thus varies by between 3 and 12 cycles.

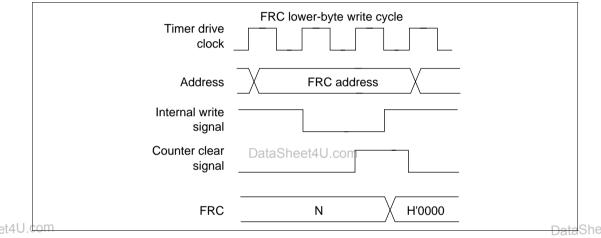

- 2. Contention between FRC Write and Clear

When a counter clear signal is generated with the timing shown in figure 11.14 during the write cycle for the lower byte of FRC, writing does not occur to the FRC, and the FRC clear takes priority.

Figure 11.14 Contention between FRC Write and Clear

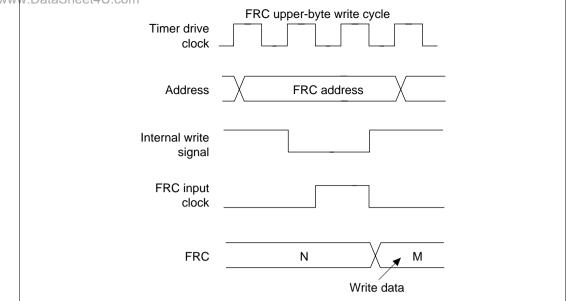

3. Contention between FRC Write and Increment

When an increment occurs with the timing shown in figure 11.15 during the write cycle for the lower byte of FRC, no increment is performed and the counter write takes priority.

DataSheet4U.com

# Figure 11.15 Contention between FRC Write and Increment

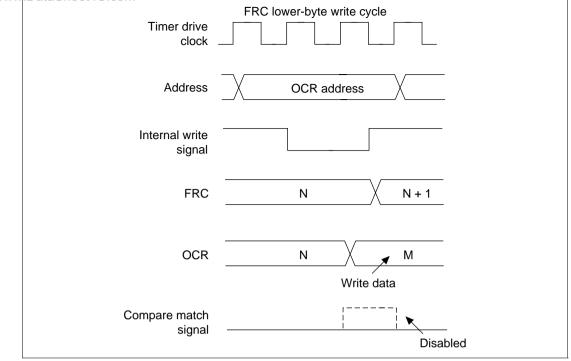

4. Contention between OCR Write and Compare Match

When a compare match occurs with the timing shown in figure 11.16, during the write cycle for the lower byte of OCRA or OCRB the OCR write takes priority and the compare match signal is disabled.

et4U.com

DataShe

DataSheet4U.com

www.DataSheet4L

Figure 11.16 Contention between OCR and Compare Match

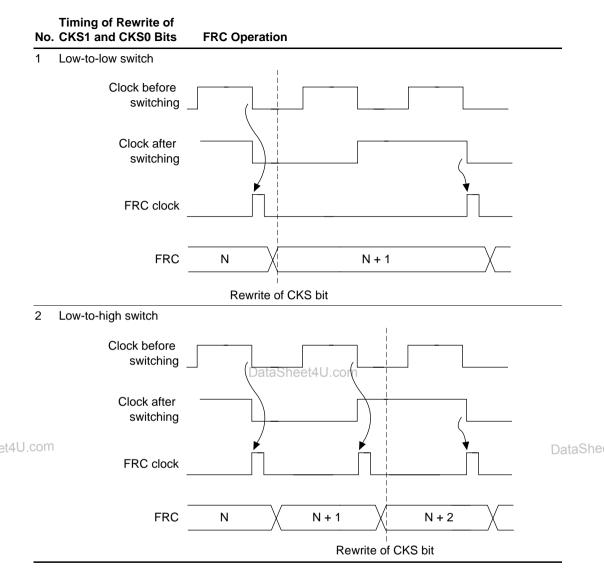

5. Internal Clock Switching and Counter Operation

FRC will sometimes begin incrementing because of the timing of switching between internal clocks. Table 11.4 shows the relationship between internal clock switching timing (CKS1 and DataShe

et4U.com CKS0 bit rewrites) and FRC operation.

When an internal clock is used, the FRC clock is generated when the falling edge of an internal clock (created by dividing the system clock  $(\phi)$ ) is detected. When a clock is switched to high before the switching and to low after switching, as shown in case 3 in table 11.4, the switchover is considered a falling edge and an FRC clock pulse is generated, causing FRC to increment. FRC may also increment when switching between an internal clock and an external clock.

# www.DataSheet4U.com Table 11.4 Internal Clock Switching and FRC Operation

DataSheet4U.com

www.DataSheet4U.com

316 DataSheet4U.com

### www.DataSheet4U.com Table 11.4 Internal Clock Switching and FRC Operation (cont)

### 6. Timer Output (FTOA, FTOB)

During a power-on reset, the timer outputs (FTOA, FTOB) will be unreliable until the oscillation stabilizes. The initial value is output after the oscillation settling time has elapsed.

DataSheet4U.com

www.DataSheet4U.com

www.DataSheet4U.com

DataSheet4U.com

et4U.com

DataShe

DataSheet4U.com

www.DataSheet4U.com

318 DataSheet4U.com

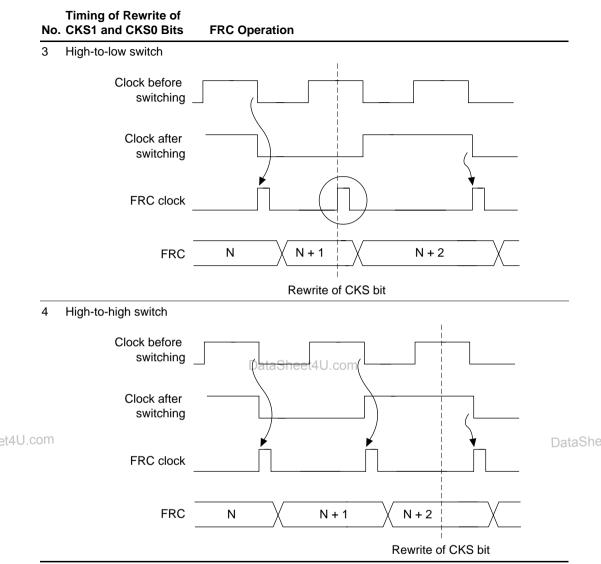

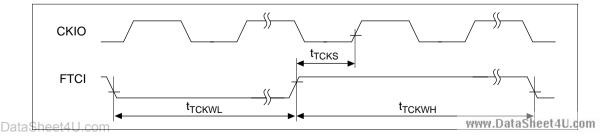

# Section 12 Watchdog Timer (WDT)

# 12.1 Overview

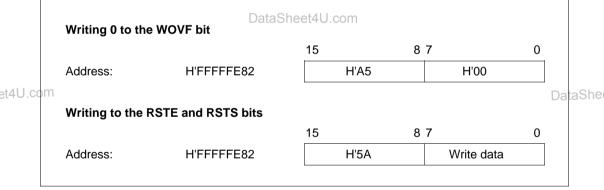

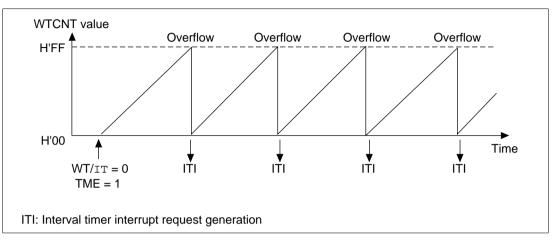

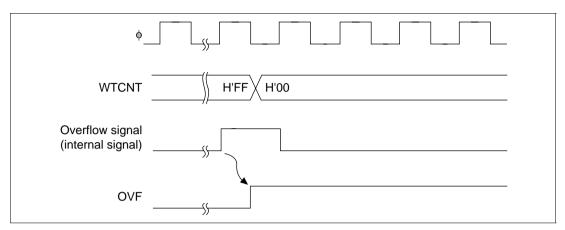

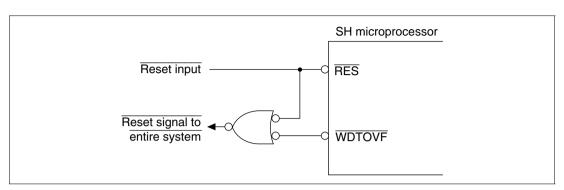

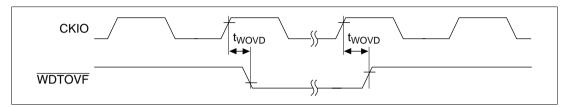

The SH7604 has a single-channel watchdog timer (WDT) for monitoring system operations. If a system becomes uncontrolled and the timer counter overflows without being rewritten correctly by the CPU, an overflow signal ( $\overline{WDTOVF}$ ) is output externally. The WDT can simultaneously generate an internal reset signal for the entire chip.

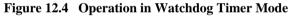

When this watchdog function is not needed, the WDT can be used as an interval timer. In the interval timer operation, an interval timer interrupt is generated at each counter overflow. The WDT is also used when recovering from standby mode, in modifying a clock frequency, and in clock pause mode.

#### 12.1.1 Features

- Works in watchdog timer mode or interval timer mode.

- Outputs WDTOVF in watchdog timer mode. When the counter overflows in watchdog timer mode, overflow signal WDTOVF is output externally. It is possible to select whether to reset the chip internally when this happens. Either the power-on reset or manual reset signal can be selected as the internal reset signal.

- Generates interrupts in interval timer mode. When the counter overflows, it generates an interval timer interrupt.

- Used for standby mode clearing, clock frequency modification, and clock pause mode.

- Works with eight counter clock sources.

t4U.com

DataShe

DataSheet4U.com

Figure 12.1 shows a block diagram of the WDT.

#### **12.1.3 Pin Configuration**

Table 12.1 shows the pin configuration.

#### Table 12.1Pin Configuration

|    | Pin                     | Abbreviation | I/O | Function                                             |

|----|-------------------------|--------------|-----|------------------------------------------------------|

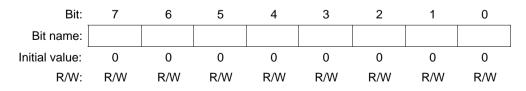

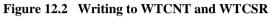

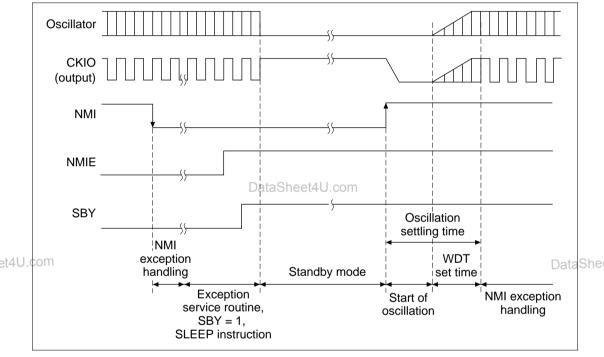

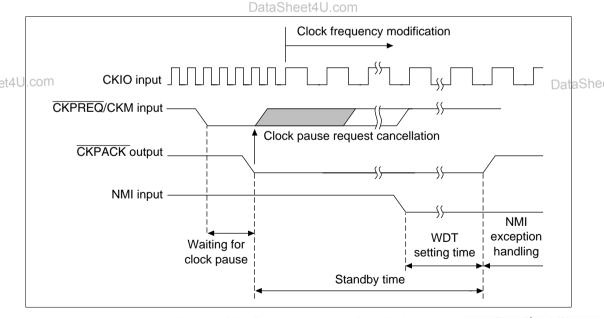

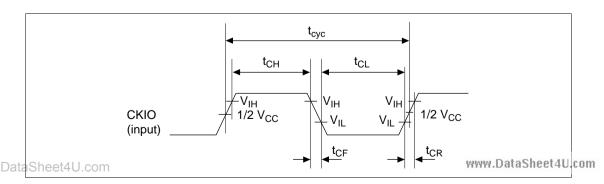

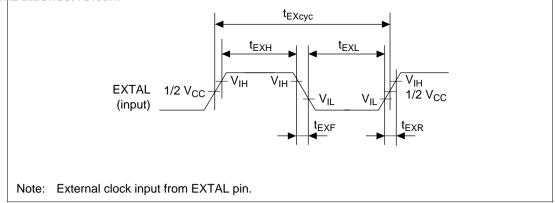

|    | Watchdog timer overflow | WDTOVF       | 0   | Outputs the counter overflow signal in watchdog mode |