#### DISTINCTIVE CHARACTERISTICS

- High density 4096 x 1 organization

- High output drive two full TTL loads

- TTL compatible interface (except CE)

- Low power dissipation —

400 mW typ., 750 mW max. operating 5.0 mW typ., 13 mW max. refresh only 0.1 mW typ., 3.0 mW max. standby

- Low I<sub>DD</sub> current surges easier decoupling

- Low V<sub>CC</sub> current drain 10μA

- Simplified timing requirements —

Zero data hold with respect to CE

Optional data hold with respect to R/W

Optional data set-up with respect to R/W

- Low clock capacitance –20pF max.

- Unique fully capacitive input circuits eliminate extraneous current surges

- Direct plug-in replacement for TMS4060

- N-channel silicon gate MOS technology

- 100% MIL-STD-883 reliability assurance testing

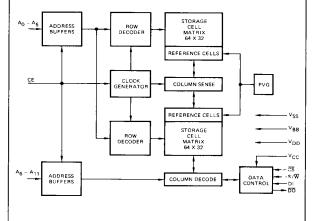

#### **FUNCTIONAL DESCRIPTION**

The Am9060 devices are high performance, 4k-bit, dynamic, read/write, random access memories. They are organized as 4096 words by 1-bit per word. The basic memory element is a one-transistor cell that stores charge on a small internal capacitor. The memory mechanism is dynamic and the chip should be periodically refreshed in order to maintain stored data integrity.

All input signals are fully TTL compatible, except the single high-level clock signal called Chip Enable. When CE goes low the memory is internally precharged and then assumes its low power standby mode. All operating cycles are initiated when CE goes high. Read-out is nondestructive so simple read or write operations are normally performed. Successive operations at the same location can be designed to improve performance since readdressing is not required. The most useful double operation combination is specified as a Read/Modify/Write cycle.

The output buffer will drive two standard TTL loads. The buffer is a three-state totem-pole configuration and exhibits a high output impedance when CE is low or when the chip is unselected. Output data polarity is inverted relative to the input data.

#### **BLOCK DIAGRAM**

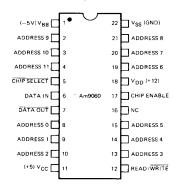

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

#### ORDERING INFORMATION

| Ambient Temperature<br>Specification |              | Access Time |           |           |  |  |  |

|--------------------------------------|--------------|-------------|-----------|-----------|--|--|--|

|                                      |              | 300 ns      | 250 ns    | 200 ns    |  |  |  |

| 0°C ≤ T <sub>A</sub> ≤ +70°C         | Molded DIP   | AM9060CPC   | AM9060DPC | AM9060EPC |  |  |  |

|                                      | Hermetic DIP | AM9060CDC   | AM9060DDC | AM9060EDC |  |  |  |

# Am9060

# MAXIMUM RATINGS above which useful life may be impaired

| Storage Temperature                                        | -65°C to +150°C  |

|------------------------------------------------------------|------------------|

| Ambient Temperature Under Bias                             | 0°C to +70°C     |

| All Supply Voltages with Respect to V <sub>BB</sub>        | -0.3 V to +20 V  |

| All Input Signal Voltages with Respect to V <sub>BB</sub>  | -0.3 V to +20 V  |

| Output Voltage with Respect to V <sub>SS</sub> , Operating | -2.0 V to +7.0 V |

| Power Dissipation                                          | 1.0W             |

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages.

### **OPERATING RANGE**

| Ambient Temperature | $V_{DD}$  | Vcc         | V <sub>SS</sub> V <sub>BB</sub> 05.0 ∨ ± 10 <sup>o</sup> |             |

|---------------------|-----------|-------------|----------------------------------------------------------|-------------|

| 0°C to +70°C        | +12V ± 5% | +5.0 V ± 5% | 0                                                        | 5.0 V ± 10% |

No signal or supply voltage should ever be more than 0.3 V more negative than  $\ensuremath{\text{V}_{\text{BB}}}.$

# **ELECTRICAL CHARACTERISTICS** over operating range (note 1)

| arameters            | Description                            | Test Conditions                                                                                          |                 | Min.                 | Тур. | Max.                 | Units |  |

|----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|----------------------|------|----------------------|-------|--|

| v <sub>OH</sub>      | Output HIGH Voltage                    | I <sub>OH</sub> = -2.0mA                                                                                 |                 | 2.4                  |      | Vcc                  | Volts |  |

| VOL                  | Output LOW Voltage                     | 1 <sub>OL</sub> = 3.2mA                                                                                  | V <sub>SS</sub> |                      | 0.4  | Volts                |       |  |

| V <sub>IH</sub>      | Input HIGH Voltage<br>(Except CE)      |                                                                                                          |                 | 2.4                  |      | Vcc                  | Volts |  |

| VIL                  | Input LOW Voltage<br>(Except CE)       |                                                                                                          |                 | -0.6                 |      | 0.8                  | Volts |  |

| V <sub>IH</sub> (CE) | Chip Enable Input HIGH Voltage         |                                                                                                          |                 | V <sub>DD</sub> −0.6 |      | V <sub>DD</sub> +1.0 | Volts |  |

| VIL(CE)              | Chip Enable Input LOW Voltage          |                                                                                                          |                 | -1.0                 |      | 0.8                  | Volts |  |

| կ                    | Input Load Current (Except CE)         | V <sub>SS</sub> ≤ V <sub>1</sub> ≤ V <sub>CC</sub>                                                       |                 |                      |      | 10                   | μΑ    |  |

| II(CE)               | Input Load Current, CE                 | -1.0 V ≤ V <sub>I(CE)</sub> ≤ 13.2 V                                                                     |                 |                      |      | 2.0                  | μΑ    |  |

| loz                  | Output Leakage Current                 | -0.6V ≤ V <sub>O</sub> ≤ V <sub>CC</sub><br>CE = V <sub>IL</sub> (CE) or <del>CS</del> = V <sub>IH</sub> |                 |                      |      | 10                   | μΑ    |  |

| ¹cc                  | VCC Supply Current (Note 7)            | CE = VIL (CE) or CS = VIH                                                                                |                 |                      |      | 10                   | μА    |  |

|                      |                                        | VIH(CE) = 12.6 V                                                                                         |                 |                      | 32   | 60                   | mA    |  |

| ססי                  | V <sub>DD</sub> Supply Current         | VIL(CE) = 0.6 V                                                                                          |                 |                      | 10   | 200                  | μΑ    |  |

|                      |                                        |                                                                                                          |                 | Am9060C              |      | 29                   | 60    |  |

|                      |                                        | Read or Write cycle minimum cycle time                                                                   | Am9060D         |                      | 31   | 60                   | mA    |  |

|                      |                                        | minimum cycle time                                                                                       | Am9060E         |                      | 32   | 60                   |       |  |

| IDD(AV)              | Average V <sub>DD</sub> Supply Current |                                                                                                          | Am9060C         |                      | 29   | 60                   |       |  |

|                      |                                        | Read/Modify/Write cycle                                                                                  | Am9060D         |                      | 31   | 60                   |       |  |

|                      |                                        | minimum cycle time                                                                                       | Am9060E         |                      | 32   | 60                   |       |  |

| 1 <sub>BB</sub>      | V <sub>BB</sub> Supply Current         | V <sub>BB</sub> = -5.5 V, V <sub>DD</sub> = 12.6 V<br>V <sub>CC</sub> = 5.25 V, V <sub>SS</sub> = 0 V    |                 |                      | -5.0 | -100                 | μΑ    |  |

| C |  |  |  |  |

|---|--|--|--|--|

|   |  |  |  |  |

| Parameters         | Description                                 | Test Condit                                                                                                                    | Test Conditions                 |     | Max. | Units |

|--------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|------|-------|

| C <sub>i(AW)</sub> | (Address and Write)                         |                                                                                                                                |                                 | 5.0 | 7.0  | pF    |

| c <sub>i(CD)</sub> | Input Capacitance<br>(Chip Select and Data) | V <sub>DD</sub> = 12V, V <sub>SS</sub> = 0V<br>V <sub>BB</sub> = -5.0V, V <sub>CC</sub> = 5.0V<br>All inputs = 0V<br>f = 1 MH2 |                                 | 3.0 | 5.0  | pF    |

| C <sub>i(CE)</sub> | Input Capacitance<br>(Chip Enable)          |                                                                                                                                | V <sub>I(CE)</sub> = -1.0, 10.8 | 15  | 20   | pF    |

| c <sub>O</sub>     | Output Capacitance                          |                                                                                                                                |                                 | 3.0 | 5.0  | pF    |

Am9060E

Min. Max. Units

Am9060C

Max.

Am9060D

Min. Max.

Description

**Parameters**

| tR                   | Column Refresh Interval          |               |                                     |            | 2.0  |                                                  | 2.0          | 1          | 20   | Г  |

|----------------------|----------------------------------|---------------|-------------------------------------|------------|------|--------------------------------------------------|--------------|------------|------|----|

|                      | <u> </u>                         |               |                                     |            | 2.0  |                                                  | 2.0          |            | 2.0  | ms |

| Read Cycle           | ,                                |               |                                     | 470        |      |                                                  |              | ,          | ,    |    |

| tc(rd)               | Read Cycle Time                  | CE transition | CE transition time ≤ 20ns           |            |      | 430                                              |              | 400        |      | ns |

| tw(CEH)              | Chip Enable HIGH Pulse Width     |               | 300<br>130                          | 4000       |      | 4000                                             | 230          | 4000       | ns   |    |

| tw(CEL)              | Chip Enable LOW Pulse Width      |               |                                     |            |      | 130                                              |              | 130        |      | ns |

| tsu(ad)              | Address Set-up Time              |               |                                     |            |      | 0                                                |              | 0          |      | ns |

| t <sub>su</sub> (CS) | Chip Select Set-up Time          | Chie          | Enable                              | 0          | ļ    | 0                                                |              | 0          |      | ns |

| t <sub>su(rd)</sub>  | Read Set-up Time                 |               | times ≤40 ns                        | 0          |      | 0                                                |              | 0          |      | ns |

| th(ad)               | Address Hold Time                |               |                                     | 125        |      | 100                                              |              | 100        |      | ns |

| th(CS)               | Chip Select Hold Time            |               |                                     | 125        |      | 100                                              |              | 100        |      | ns |

| th(rd)               | Read Hold Time                   |               | _                                   | 0          |      | 0                                                |              | 0          |      | ns |

| tPZL                 | Chip Enable to Output ON Delay   | Output load:  |                                     |            | 175  |                                                  | 150          |            | 125  | ns |

| tPOZ                 | Chip Enable to Output OFF Delay  | one standard  |                                     | 30         |      | 30                                               |              | 30         |      | ns |

| ta(CE)               | Chip Enable Access Time (Note 6) | TTL gate      | Chip enable                         |            | 280  |                                                  | 230          |            | 180  | ns |

| ta(ad)               | Address Access Time (Note 6)     | plus 50pF     | rise time ≤20 ns                    |            | 300  |                                                  | 250          |            | 200  | ns |

| rite Cycle           | •                                |               |                                     |            |      |                                                  |              |            |      |    |

| t <sub>c(wr)</sub>   | Write Cycle Time                 | CE transition | time ≤ 20 ns                        | 470        |      | 430                                              |              | 400        |      | ns |

| tw(CEH)              | Chip Enable HIGH Pulse Width     |               |                                     |            | 4000 | 260                                              | 4000         | 230        | 4000 | ns |

| tw(CEL)              | Chip Enable LOW Pulse Width      |               |                                     | 130        | _    | 130                                              |              | 130        |      | ns |

| tw(wr)               | Write Pulse Width                |               |                                     | 200        | -    | 190                                              |              | 180        |      | ns |

| t <sub>su(ad)</sub>  | Address Set-up Time              |               |                                     | 0          | -    | 0                                                | <u> </u>     | 0          |      | ns |

| t <sub>su</sub> (CS) | Chip Select Set-up Time          |               | Enable<br>times ≤40 ns              | 0          | -    | 0                                                |              | 0          |      | ns |

| t <sub>su(da)</sub>  | Data In Set-up Time              | transition    | times «40ns                         | 180        |      | 170                                              |              | 160        |      | ns |

| t <sub>su(wr)</sub>  | Write Pulse Set-up Time          |               |                                     | 240        | -    | 220                                              |              | 210        |      | ns |

| th(ad)               | Address Hold Time                |               |                                     | 125        |      | 100                                              | <del> </del> | 100        |      | ns |

| th(CS)               | Chip Select Hold Time            |               |                                     | 125        | -    | 100                                              |              | 100        |      | ns |

| th(da)               | Data In Hold Time (Note 2)       |               |                                     | 0 (30)     |      | 0 (20)                                           |              | 0 (10)     |      | ns |

| ead/Modif            | fy/Write Cycle                   |               |                                     |            |      | L                                                |              |            |      |    |

| t <sub>c</sub> (RMW) | Read/Modify/Write Cycle Time     | CE transition | time and                            | 710        |      | 640                                              |              | 580        |      | ns |

| tw(CEH)              | Chip Enable HIGH Pulse Width     |               | ill time ≤ 20ns                     | 540        | 4000 | 470                                              | 4000         | 410        | 4000 | ns |

| tw(CEL)              | Chip Enable LOW Pulse Width      |               |                                     | 130        | 1000 | 130                                              | 7000         | 130        | 4000 | ns |

| tw(wr)               | Write Pulse Width                |               |                                     | 200        |      | 190                                              |              | 180        |      | ns |

| t <sub>su(ad)</sub>  | Address Set-up Time              |               |                                     | 0          |      | 0                                                |              | 0          |      |    |

| t <sub>su</sub> (CS) | Chip Select Set-up Time          |               |                                     | 0          |      | 0                                                |              | 0          |      | ns |

| t <sub>su(da)</sub>  | Data In Set-up Time              |               |                                     | 180        |      | 170                                              |              | 160        |      | ns |

| t <sub>su(rd)</sub>  | Read Set-up Time                 |               |                                     | 0          |      | <del>                                     </del> |              |            |      | ns |

| t <sub>su(wr)</sub>  | Write Pulse Set-up Time          | -             |                                     | 240        |      | 0<br>220                                         |              | 0<br>210   |      | ns |

| th(ad)               | Address Hold Time                |               | Chip Enable transition times ≤40 ns |            |      |                                                  |              |            |      | ns |

| th(CS)               | Chip Select Hold Time            |               |                                     | 125<br>125 | -    | 100                                              |              | 100<br>100 |      | ns |

| th(rd)               | Read Hold Time                   |               |                                     |            |      |                                                  |              |            |      | ns |

| th(da)               | Data In Hold Time (Note 2)       |               |                                     | 280        |      | 230                                              |              | 180        |      | ns |

| tPZL                 | Chip Enable to Output ON Delay   |               | 1                                   | 0 (30)     |      | 0 (20)                                           |              | 0 (10)     |      | ns |

| tPOI                 | Write to Output Invalid Delay    | Output load:  |                                     |            | 175  |                                                  | 150          |            | 125  | ns |

| tPOZ                 |                                  | one standard  |                                     | 30         |      | 30                                               |              | 30         |      | ns |

| 102                  | Chip Enable to Output OFF Delay  | TTI coto      |                                     | 30         |      | 30                                               |              | 30         | [    | ns |

**Test Conditions**

ta(CE)

ta(ad)

- Typical values are at  $T_A = 25^{\circ}$ C, nominal supply voltages and nominal processing parameters.

Data Hold time ( $t_{h(da)}$ ) may be optionally specified with respect to either the rising edge of Read/Write or the falling edge of Chip Enable. The zero value shown in the Characteristics table is with respect to Chip Enable. Data hold time with respect to Read/Write is shown in parenthesis.

Chip Enable

rise time ≤20ns

280

300

230

250

ns

ns

180

200

- Input signal (except Chip Enable) timing references are 0.6 V and 2.2 V.

- Chip Enable timing references are at 10% and 90% of V<sub>IH</sub>(CE). Output timing references are 0.4V and 2.4V.

Address Access Time (Note 6)

Chip Enable Access Time

- Slope of access time versus load capacitance is approximately 0.1ns/pF.

- V<sub>CC</sub> supplies the final output transistor only. Except for leakage, V<sub>CC</sub> supply current during CE on is dependent on output loading only.

TTL gate

plus 50 pF

#### APPLICATION INFORMATION

#### **INTERFACE SIGNALS**

The 12 Address inputs are used to specify one of  $2^{12}$  locations within the memory ( $2^{12}$  = 4096). The Chip Select signal acts as a high order address so that several memory chips may be operated together for capacities greater than 4k words. Registers are included on chip for the Chip Select and Address signals in order to simplify system timing requirements. After the Chip Select input has been latched by the rising edge of CE, the select status of the chip cannot be altered by changing the state of Chip Select line. Chip Select only affects the data control circuitry.

The Data In signal timing is specified relative to the rising edge of  $R/\overline{W}$ . The Data In and Read/Write circuitry are static and the input data set-up requirement is independent of the write pulse width. The hold time for input data may be timed relative to either  $R/\overline{W}$  or to CE, for extra flexibility in system design.

The Read/Write line controls the type of operation being performed. It may be thought of as a normally high signal that is pulsed low when writing is desired. The normally high state prevents unintentional modification of data.  $R/\overline{W}$  should also be high during all refresh operations, unless Chip Select is high.

The Chip Enable input is a high level clock signal that controls the basic timing of all internal operations. When CE is low the memory enters the standby mode and dissipates very little power. Active operations begin when CE goes high. In a memory system with an array of storage chips, it is usually the case that only a few devices will be active at any one time, thus keeping the average power dissipation at very low levels.

The Data Out circuitry is three-state and designed to permit wired-OR connection of several chips for greater memory depth than 4k. Unclocked or unselected devices will have high impedance outputs, allowing a selected and clocked device to dominate the output data bus. The output data is inverted relative to the input data; that is, information written in as a logic one will be read out as a logic zero. Valid output is always preceded by a period of low output data.

All input circuitry in the Am9060 memories is purely capacitive and does not cause clock related current surges to flow in the input lines. This feature improves noise immunity margins and helps simplify input driving requirements.

Current surges occur in the V<sub>DD</sub> and V<sub>BB</sub> supplies in conjunction with both the rising and falling transitions of Chip Enable. Both voltages must be carefully decoupled to V<sub>SS</sub> to prevent the current spikes from generating excessive noise.

#### REFRESH

Information is stored as the presence or absence of charge within each internal cell. Leakage currents eventually drain away any charge present in a cell and information is lost. To prevent data loss, a cell can have its charge level restored before too much charge has leaked off. Each cell must be refreshed at least once every 2 ms, worst case.

The 4096 cells in the memory matrix are organized as an array of 64 rows and 64 columns. When any cell within a row is actively cycled, all 64 locations in the row are refreshed. Thus the refresh requirement is met if all 64 rows are accessed every 2 ms. Address lines Aq through A5 specify the rows.

The Chip Select input only controls the Data Out and Read/Write circuitry so that a chip need not be selected in order to be refreshed. This allows parallel refreshing of many devices without causing contention on output busses.