**Preliminary**

JULY 1978

# **INS8253 Programmable Interval Timer**

## **General Description**

The INS8253 is a programmable timer/counter device contained in a standard, 24-pin dual-in-line package. The chip, which is fabricated using N-channel silicon gate technology, provides counting or time-out services in a microcomputer system. The various operating modes and other functional characteristics of the INS8253 are programmed by the system software.

The INS8253 provides three independent 16-bit down counters, each of which is capable of count rates in the range DC to 2MHz. Through software initialization, each counter can be made to operate in any one of six modes. The modulus and counting system used are also specified by system software. The operating characteristics of any individual counter can be modified by the software at any time to meet changing system requirements.

The modulus of any given counter can be changed at the program's discretion by loading a new value into the counter. A counter load operation may be limited to the counter's least significant byte or to its most significant byte, or it may revise both halves of the counter.

Count sequences may be in either binary or BCD. This choice is also individually specified for each counter by the software.

The contents of each counter may be read either directly or through an auxiliary register. A direct reading of the counter can be made whenever the counter is inhibited from counting. A count value can also be read without interfering with the counting process. This is done by transferring the counter's current value to an auxiliary register and then reading that register. This counter-to-register transfer can be executed without affecting the normal count sequence.

## **Features**

- 3 Individually Programmable 16-Bit Counters

- · 6 Operating Modes

- DC to 2MHz Count Rates

- Individual Count Rate and Modulus for Each Counter

- Selectable Counting System (Binary or BCD) for Each Counter

- TRI-STATE® TTL Drive Capability for Bidirectional Data Bus

- Single +5 Volt Power Supply

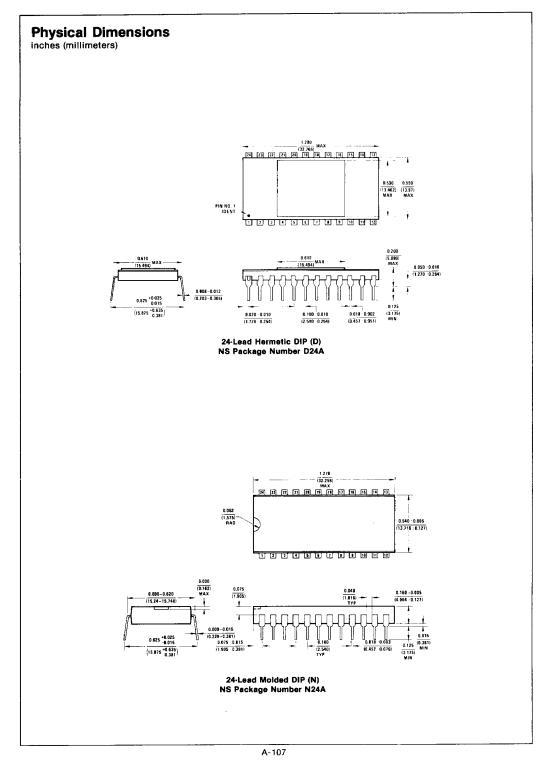

- 24-Pin Dual-in-Line Package

- MICROBUS™\* Compatible

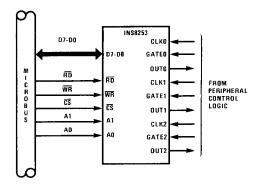

# **INS8253 MICROBUS Configuration**

\*A trademark of National Semiconductor Corporation.

© 1978 National Semiconductor Corp

## **Absolute Maximum Ratings**

Ambient Temperature Under Bias ...0°C to +70°C

Maximum Voltage to Any Input

with Respect to GND .... -0.5V to +7V

Storage Temperature .... -65°C to +150°C

Power Dissipation .... 1 Watt

Note: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC Electrical Characteristics.

## **DC Electrical Characteristics**

$(T_A = 0 \,{}^{\circ}\text{C to } + 70 \,{}^{\circ}\text{C}; V_{CC} = 5 \,{}^{\vee}\text{C})$

| Symbol          | Parameter                      | Min   | Max                    | Unit | Test Conditions                          |  |  |

|-----------------|--------------------------------|-------|------------------------|------|------------------------------------------|--|--|

| V <sub>IL</sub> | Input Low Voltage              | - 0.5 | 0.8                    | ٧    |                                          |  |  |

| V <sub>iH</sub> | Input High Voltage             | 2.2   | V <sub>CC</sub> + 0.5V | ٧    |                                          |  |  |

| V <sub>OL</sub> | Output Low Voltage             |       | 0.45                   | ٧    | Note 1                                   |  |  |

| V <sub>OH</sub> | Output High Voltage            | 2.4   |                        | ٧    | Note 2                                   |  |  |

| l <sub>IL</sub> | Input Load Current             | •     | ± 10                   | μА   | V <sub>IN</sub> = V <sub>CC</sub> to 0V  |  |  |

| lofL            | Output Float Leakage           |       | ± 10                   | μΑ   | V <sub>OUT</sub> = V <sub>CC</sub> to 0V |  |  |

| lcc             | V <sub>CC</sub> Supply Current |       | 140                    | mA   |                                          |  |  |

Note 1: INS8253,  $I_{OL} = 1.6 \text{ mA}$ . Note 2: INS8253,  $I_{OH} = -150 \mu \text{A}$ .

# Capacitance

$T_A = 25$ °C;  $V_{CC} = GND = 0$ V.

| Symbol           | Parameter         | Min | Max | Unit | Test Conditions                             |

|------------------|-------------------|-----|-----|------|---------------------------------------------|

| C <sub>IN</sub>  | Input Capacitance |     | 10  | pF   | f <sub>C</sub> = 1MHz                       |

| C <sub>I/O</sub> | I/O Capacitance   |     | 20  | pF   | Unmeasured pins returned to V <sub>SS</sub> |

# **AC Electrical Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = 5.0 \text{V} \pm 5\%$ ; GND = 0V

## **Bus Parameters:**

| Symbol          | Parameter                     | Min | Max | Unit |

|-----------------|-------------------------------|-----|-----|------|

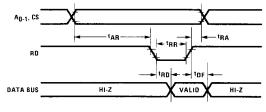

| READ CYCLI      | E                             |     |     |      |

| t <sub>AR</sub> | Address Stable Before READ    | 50  |     | ns   |

| t <sub>RA</sub> | Address Hold Time for READ    | 5   |     | ns   |

| t <sub>RR</sub> | READ Pulse Width              | 400 |     | ns   |

| t <sub>RD</sub> | Data Delay from READ (Note 2) |     | 300 | ns   |

| t <sub>DF</sub> | READ to Data Floating         | 25  | 125 | ns   |

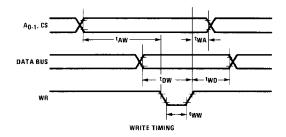

| WRITE CYCL      | E                             |     | •   |      |

| t <sub>AW</sub> | Address Stable Before WRITE   | 50  |     | ns   |

| t <sub>WA</sub> | Address Hold Time for WRITE   | 30  |     | ns   |

| t <sub>WW</sub> | WRITE Pulse Width             | 400 |     | ns   |

| t <sub>DW</sub> | Data Setup Time for WRITE     | 300 |     | ns   |

| t <sub>WD</sub> | Data Hold Time for WRITE      | 40  |     | ns   |

| t <sub>RV</sub> | Recovery Time Between WRITEs  | 1   |     | ns   |

Note 1: AC timings measured at  $V_{OH} = 2.2V$ ,  $V_{OL} = 0.8V$ .

Note 2: Test conditions: INS8253,  $C_L = 100 \, pF$ .

# **Input Waveforms for AC Tests**

READ TIMING

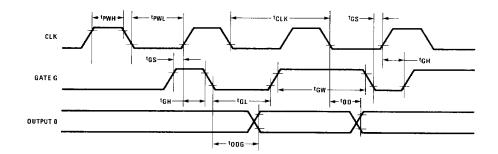

# **Clock and Gate Timing**

| Symbol           | Parameter                            | Min  | Max | Unit |

|------------------|--------------------------------------|------|-----|------|

| t <sub>CLK</sub> | Clock Period                         | 380  | DC  | ns   |

| t <sub>PWH</sub> | High Pulse Width                     | .230 |     | ns   |

| t <sub>PWL</sub> | Low Pulse Width                      | 150  |     | ns   |

| t <sub>GW</sub>  | Gate Width High                      | 150  |     | ns   |

| t <sub>GL</sub>  | Gate Width Low                       | 100  |     | ns   |

| t <sub>GS</sub>  | Gate Setup Time to CLK †             | 100  |     | ns   |

| t <sub>GH</sub>  | Gate Hold Time After CLK↑            | 50   |     | ns   |

| top              | Output Delay From CLK↓<br>(Note 1)   |      | 400 | ns   |

| topg             | Output Delay From Gate ↓<br>(Note 1) |      | 300 | ns   |

Note 1: Test conditions: INS8253,  $G_L = 100\,pF$ .

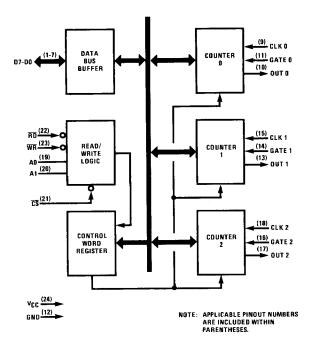

## **INS8253 Functional Block Diagram**

# **INS8253 Functional Pin Description**

The following describes the functions of all INS8253 input/output pins. Some of these descriptions refer to internal circuits.

## NOTE

In the following descriptions, a low represents a logic 0 (0 Volt, nominal) and a high represents a logic 1 (+2.4 Volts, nominal).

#### INPUT SIGNALS

Chip Select (CS): When low, the chip is selected. This enables communication between the INS8253 and the microprocessor.

Read (RD): When low, allows the microprocessor to read contents of counter specified by A0, A1.

Write (WR): When low, writes control word into control word register or loads new count value into selected counter. Destination of data (control word register or counter 0, 1 or 2) is specified by A0, A1.

A0, A1: These inputs are used to select one of the counters for reading or writing or to select the control word register for writing. A0, A1 may be controlled via address bus lines.

Clock (CLK0-CLK2): Each counter has a separate clock input that drives the counter.

Gate (Gate 0 - Gate 2): Each counter is individually controlled by a separate Gate input (1 = enable, 0 = inhibit). In some modes, the positive edge of Gate is used to initiate the counting process. Specific use of Gate depends on the counter's operating mode Details are provided in the section entitled INS8253 Programming.

#### **OUTPUT SIGNALS**

Output (Out 0-Out 2): Each counter has a single output that indicates whether or not the counter has reached its terminal count. Specific operation of this output depends on the counter's mode. Details are provided in the section entitled INS8253 Programming.

## INPUT/OUTPUT SIGNALS

Data (D7-D0) Bus: This bus, which comprises eight TRI-STATE input/output lines, provides for bidirectional communication between the INS8253 and the microprocessor. Control words and count value bytes are transferred over these lines.

## **INS8253 Pin Configuration**

# **INS8253 Programming**

This section provides basic information for programming the INS8253 and describes the methods for reading counter status. Table 1 summarizes the control signals needed to write command words and new count values into the INS8253 and to read the contents of individual counters.

Table 1. Bus Control for INS8253 I/O Operations

| <b>Output Operations</b> | $\overline{cs}$ | $\overline{\mathbf{w}}_{\mathbf{R}}$ | RD | <b>A</b> 1 | A0 |

|--------------------------|-----------------|--------------------------------------|----|------------|----|

| LOAD COUNTER 0           | 0               | 0                                    | 1  | 0          | 0  |

| LOAD COUNTER 1           | 0               | 0                                    | 1  | 0          | 1  |

| LOAD COUNTER 2           | 0               | 0                                    | 1  | 1          | 0  |

| WRITE CONTROL WORD       | 0               | 0                                    | 1  | 1          | 1  |

| Input Operations         |                 |                                      |    |            |    |

| READ COUNTER 0           | 0               | 1                                    | 0  | 0          | 0  |

| READ COUNTER 1           | 0               | 1                                    | 0  | 0          | 1  |

| READ COUNTER 2           | 0               | 1                                    | 0  | 1          | 0  |

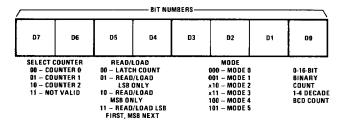

#### WRITING CONTROL WORDS

Each counter's mode and counting system (binary or BCD) are specified by an eight-bit control word. See figure 1. An I/O write operation with A0, A1 = 11 will load the control word into the control word register. The control word contains four fields:

- D7, D6 (SC1, SC0) This field specifies which counter will be affected by the other control fields.

- D5, D4 (RL1, RL0) A bit pattern of 00 in this field causes the contents of the selected counter to be latched in an auxiliary register. The count value can then be read without inhibiting the counter. The other three bit patterns specify which byte(s) of the selected counter will be affected by any subsequent read/write operations addressed to that counter.

- D3, D2, D1 (M2, M1, M0) This field specifies the mode of operation for the selected counter.

- D0 (BCD) This one-bit field specifies the counting system to be used by the selected counter.

Any time after a counter is initialized by a control word, its initial count value can be loaded. This is done by means of a write operation addressed to that counter. Details are given in the section entitled Loading Initial Count Value

Programming of the three counters can be executed in any sequence, with only two requirements.

- A counter must be issued a control word before it is given an initial count value.

- Read and write operations addressed to a counter must conform to the byte-selection rules specified by the RL1, RL0 field in the control word. For example, if the counter's RL1, RL0 bits = 10, subsequent counter load operations addressed to that counter must be intended for the most significant byte only.

Figure 1. Control Word Format

## **COUNTER MODE DESCRIPTIONS**

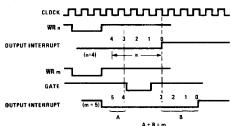

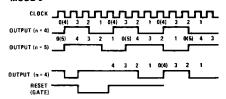

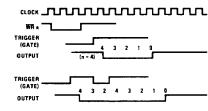

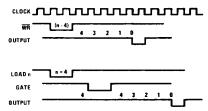

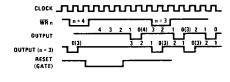

Figure 2 provides timing information for the six INS8253 operating modes.

Mode 0, Timed Interrupt — In this mode, OUT goes low when the mode is set. The counter begins counting CLK cycles when the count is loaded. OUT remains low until the terminal count is reached, at which point it goes high and remains high until either the mode or count is reloaded. The gate input will inhibit the count when low.

If the counter is loaded with a new value during a count cycle, counting will stop when the first byte is loaded and will begin decrementing from the new value after the second byte is loaded.

Mode 1, Retriggerable One Shot — In this mode, OUT goes low on the first CLK after a rising transition on Gate. OUT goes high again on the terminal count. Gate can be used to retrigger the counter. Each positive transition of Gate causes the counter to begin decrementing from the initial count value.

If a new initial count value is loaded during a count cycle, the new value will not take effect until the next rising transition of Gate.

• Mode 2, Rate Generator — In this mode, OUT goes low for one CLK cycle at the end of each count sequence. The leading edge of each pulse occurs at the start of the terminal CLK cycle. The counter will repeat count sequences as long as Gate remains high. Any positive transition of Gate will start a new count sequence at the initial count value. This allows the counter to be synchronized by Gate.

If a new initial count value is loaded during a count sequence, the current sequence will run to completion and the following sequence will then start at the new initial count value.

### MODE 0

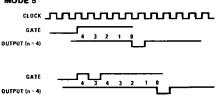

#### MODE 3

## MODE 1

## MODE 4

#### MODE 2

#### MODE 5

Figure 2. Mode Timing Waveforms

Mode 3, Square Wave Generator — In this mode, the counter generates a square wave signal at the OUT pin so long as Gate remains high. The period of the square wave is equal to one count cycle. If the initial count value is even, OUT will be high for the first half of each count sequence and low during each second half. For an odd count, OUT is high for (N + 1)/2 counts and low for (N - 1)/2 counts.

If a new initial count value is loaded during a count sequence, the current sequence will run to completion and the following sequence will then start at the new initial count value.

Any positive transition of Gate will start a new count sequence at the initial count value. This allows the counter to be synchronized by Gate.

Mode 4, Software Triggered Strobe — In this mode, OUT is normally high and goes low for one CLK cycle after the terminal count is reached. Counting is enabled when Gate is high. Counting is initiated by loading the modulus.

If a new initial count value is loaded during a count sequence, the current sequence will run to completion and the following sequence will then start at the new initial count value.

A low on the Gate input inhibits the count.

Mode 5, Hardware Triggered Strobe — In this mode, any positive transition of Gate will initiate a new count sequence. OUT then goes low for one CLK cycle when the terminal count is reached.

#### LOADING INITIAL COUNT VALUE

Each counter's modulus is determined by presetting the counter to the desired value. This is done by means of one or two I/O write operations with A1, A0 selecting the counter to be preset. The write operation loads the contents of the data bus (D7-D0) into the upper or lower half of the selected counter, as determined by the control word's RL1, RL0 field. Figure 3 summarizes the various counter loading conditions.

After a counter's initial count value is loaded, it is ready for operation in the specified mode. It begins counting CLK cycles when its Gate input goes high. Each CLK decrements the enabled counter by one until the full count cycle has been completed.

The initial count value of any counter can be changed by loading a new value into the counter's:

- LSB only (RL1, RL0 = 01),

- MSB only (RL1, RL0 = 10), or

- LSB first, and then MSB (RL1, RL0 = 11).

| Read/Load<br>Conditions |     | Effect of Subsequent Write Operation |

|-------------------------|-----|--------------------------------------|

| RL1                     | RLO |                                      |

| 0                       | 1   | WR loads D7-D0 into LSB of counter   |

- selected by A1, A0.\*

WR loads D7-D0 into MSB of counter selected by A1, A0.

- 1 1 First WR loads D7-D0 into LSB of counter selected by A1, A0. Next WR loads D7-D0 into counter's MSB.

# ^A1 A0 0 0 Selects Counter 0 0 1 Selects Counter 1 1 0 Selects Counter 2

Figure 3. Initial Count Loading Summary

#### **READING COUNT VALUES**

The current status of a count sequence can be examined at any time by the program. This can be done either by reading the counter contents directly or by latching the counter contents into an auxiliary register and then reading that register.

A counter can be read directly with the following bus conditions:

|                   | RD | A1 | A0 |

|-------------------|----|----|----|

| To Read Counter 0 | 0  | 0  | 0  |

| To Read Counter 1 | 0  | 0  | 1  |

| To Read Counter 2 | 0  | 1  | 0  |

The count should remain stable during direct reading of a counter. Stability is assured by holding the Gate input low or inhibiting the CLK input (by means of external logic) for the duration of the read operation. Counter status can also be sampled without inhibiting the count sequence. This is done by issuing a control word to the counter with RL1, RL0 = 00, followed by an I/O read of that counter's location. The RL1, RL0 bits cause the contents of the addressed counter to be latched into the auxiliary register. The subsequent read operations access the auxiliary register.

When reading either a counter or the auxiliary register, the read operation must follow the format programmed for that counter by RLO and RL1. Note that issuing a latch command of RL1, RLO = 00 does not alter the previously programmed RLO and RL1.