#### DATA SHEET :

# MBM27C4001-12-X/-15-X

## CMOS 4M-BIT UV EPROM

### CMOS 4,194,304-BIT UV ERASABLE READ ONLY MEMORY

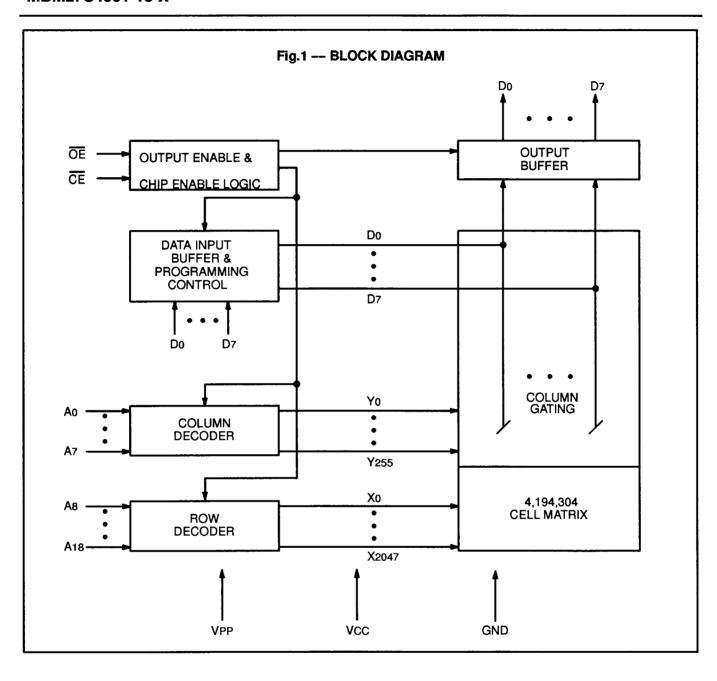

The Fujitsu MBM27C4001 EPROM is a high speed read-only memory that is UV-erasable and electrically programmable. The device contains 4,194,304 programmable or reprogrammable bits organized in a 524,288-byte/8-bit format. The MBM27C4001 is housed in a 32-pin DIP with a transparent lid; when the lid is properly exposed to an ultraviolet light source, a previously programmed bit pattern is erased in approximately 15 to 20 minutes. A new bit pattern can then be written into memory.

The MBM27C4001 EPROM is fabricated using CMOS double poly-silicon gate technology with stacked single-transistor gate cells. The MBM27C4001 is an excellent choice for system development work and in other applications where program changes are frequently necessary. Once programmed, the device requires only a single +5V power supply; the current requirements are exceptionally low in both the active and standby modes of operation.

- 524,288-byte/8-bit organization with on-chip decoding

- Single-byte or Four-byte programming capability with high-speed algorithms

- Static operation (no clocks required)

- Fast access time:

MBM27C4001-12-X = 120ns (max)MBM27C4001-15-X = 150ns (max)

- Easy and simple memory expansion via @ pin

- Three-state output for wired-OR capability

- TTL-compatible inputs/outputs

- Single =5V ( $\pm 10\%$ ) power supply with low current drain:

Active operation = 50mA (max)

Standby operation = 1.0mA(max)-TTL Level Standby operation = 100µA(max)-CMOS Level

- Fast programming: 0.1ms pulse

- Programming voltage: +12.5V

- JEDEC approved 32-pin Ceramic DIP(Suffix: Z)

### ABSOLUTE MAXIMUM RATINGS (see NOTE)

| Rating                                                   | Symbol     | Value           | Unit |

|----------------------------------------------------------|------------|-----------------|------|

| Supply Voltage with respect to GND                       | VCC        | -0.6 to +7.0    | ٧    |

| Programming Voltage with respect to GND                  | VPP        | -0.6 to +14.0   | ٧    |

| Input/Output Voltage (except for A9 with respect to GND) | VIN1, VOUT | -0.6 to VCC+0.6 | ٧    |

| Programming Voltage with respect to GND                  | VIN2       | -0.6 to +13.5   | ٧    |

| Temperature under Bias                                   | TBIAS      | -50 to +95      | °C   |

| Storage Temperature Range                                | TSTG       | -65 to +125     | °C   |

NOTE: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance

# CAPACITANCE (TA = 25° C, f = 1MHz)

| Parameter                    | Symbol | Min | Values<br>Typ | Max | Unit |

|------------------------------|--------|-----|---------------|-----|------|

| Input Capacitance (VIN=0V)   | CIN    |     | 10            | 13  | pF   |

| Output Capacitance (VOUT=0V) | Соит   |     | 7             | 10  | pF   |

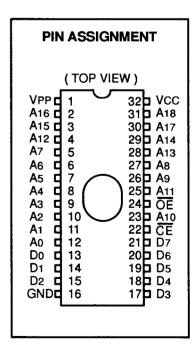

## **PIN DESCRIPTION**

| Symbol    | Pin No.                 | Function                                                                                                                              |

|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| VPP       | 1                       | +12.5V programming voltage                                                                                                            |

| ŌĒ        | 24                      | Output enable. When $\overline{OE}$ and $\overline{CE}$ are active Low strobe is active High; all output lines(D0 to D7) are enabled. |

| A0 to A18 | 2 to 12, 23<br>25 to 31 | Address lines                                                                                                                         |

| D0 to D7  | 13 to 15,<br>17 to 21   | Three-state output data lines                                                                                                         |

| GND       | 16                      | Circuit ground                                                                                                                        |

| CE        | 22                      | When active Low, the device is enabled for data read.                                                                                 |

| Vcc       | 32                      | +5V power supply                                                                                                                      |

# **FUNCTIONS AND PIN CONNECTIONS**

#### 1. Read Mode

| Symbol               | A0 to A18 | D0 to D7 | ŌĒ  | CE  | Vcc | VPP | GND |

|----------------------|-----------|----------|-----|-----|-----|-----|-----|

| Standby              | Х         | Hi-Z     | Х   | ViH | +5V | +5V | GND |

| Read                 | AIN       | DOUT     | VIL | VIL | +5V | +5V | GND |

| Output Disable       | AIN       | Hi-Z     | ViH | VIL | +5V | +5V | GND |

| Electronic Signature | A0        | CODE     | VIL | VIL | +5V | +5V | GND |

Legend: X="H" or "L"

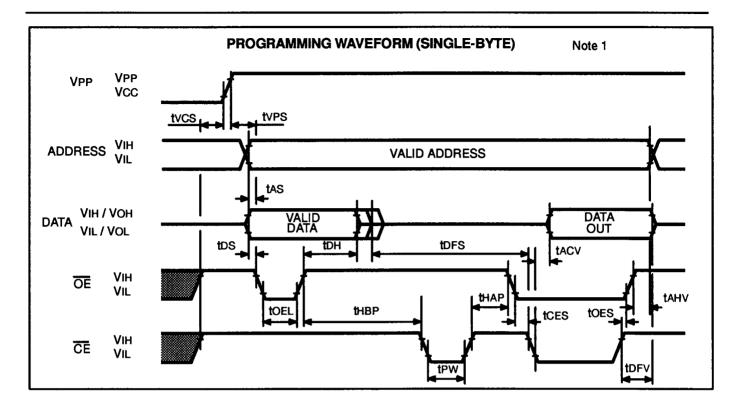

### 2. Single-Byte Programming Mode

| Symbol          | A0 to A18 | D0 to D7 | ŌĒ  | Œ   | Vcc | VPP    | GND |

|-----------------|-----------|----------|-----|-----|-----|--------|-----|

| Data Latch      | AIN       | DIN      | VIL | ViH | +6V | +12.5V | GND |

| Program         | AIN       | Hi-Z     | VIH | VIL | +6V | +12.5V | GND |

| Verify          | Ain       | DOUT     | VIL | VIL | +6V | +12.5V | GND |

| Program Inhibit | Х         | Hi-Z     | VIH | ViH | +6V | +12.5V | GND |

Legend: X='H" or "L"

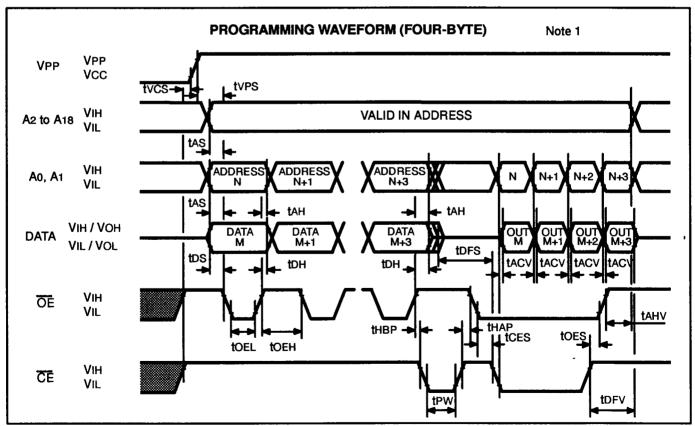

### 3. Four-Byte Programming Mode

| Symbol          | A0 , A1 | A2 to A18 | D0 to D7 | ŌĒ  | CE  | Vcc | VPP    | GND |

|-----------------|---------|-----------|----------|-----|-----|-----|--------|-----|

| Data Latch      | Ain     | AIN       | DIN      | VIL | ViH | +6V | +12.5V | GND |

| Program         | Х       | AIN       | Hi-Z     | ViH | VIL | +6V | +12.5V | GND |

| Verify          | Ain     | AIN       | DOUT     | VIL | VIL | +6V | +12.5V | GND |

| Program Inhibit | Х       | Х         | Hi-Z     | ViH | ViH | +6V | +12.5V | GND |

Legend: X='H" or "L"

## RECOMMENDED OPERATING CONDITIONS

### (Referenced to GND)

| Parameter             | Symbol | Min      | Тур | Max      | Unit |

|-----------------------|--------|----------|-----|----------|------|

| Supply Voltage        | Vcc    | 4.5      | 5.0 | 5.5      | V    |

| Supply Voltage *1     | VPP    | VCC -0.6 | Vcc | VCC +0.6 | ٧    |

| Input High Level      | ViH    | 2.0      |     | VCC +0.3 | V    |

| Input Low Level       | VIL    | -0.3     |     | 0.8      | ٧    |

| Operating Temperature | TA     | -40      |     | 85       | °C   |

<sup>\*1 :</sup> VPP supply voltage is applied posterior to or coincident with VCC supply voltage and cut off prior to or coincident with VCC supply voltage.

## DC CHARACTERISTICS

#### (Recommended operating conditions unless otherwise noted)

| Parameter              | Cumple at | Conditions               |          | Values |      |      |  |  |  |

|------------------------|-----------|--------------------------|----------|--------|------|------|--|--|--|

| Parameter              | Symbol    | Conditions               | Min      | Тур    | Max  | Unit |  |  |  |

| Input Leakage Current  | [ILI]     | VIN = VCC = 5.5V         |          |        | 10   | μΑ   |  |  |  |

| Output Leakage Current | [ILO]     | VOUT = VCC = 5.5V        |          |        | 10   | μА   |  |  |  |

| VCC Standby Current    | ISB1      | CE = VIH                 |          |        | 1.0  | mA   |  |  |  |

| VCC Standby Current    | ISB2      | CE = Vcc ±0.3V           |          |        | 100  | μА   |  |  |  |

| VCC Operation Current  | ICC       | Cycle = min., IOUT = 0mA |          |        | 50   | mA   |  |  |  |

| VPP Supply Current     | IPP       | VPP = VCC ±0.6V          |          | -      | 100  | μА   |  |  |  |

| Output High Level      | VOH1      | IOH = -400μA             | 2.4      |        |      | ٧    |  |  |  |

| Output High Level      | VOH2      | IOH = -100μA             | VCC -0.7 |        |      | ٧    |  |  |  |

| Output Low Level       | VOL       | IOL = 2.1mA              |          |        | 0.45 | ٧    |  |  |  |

## **AC CHARACTERISTICS**

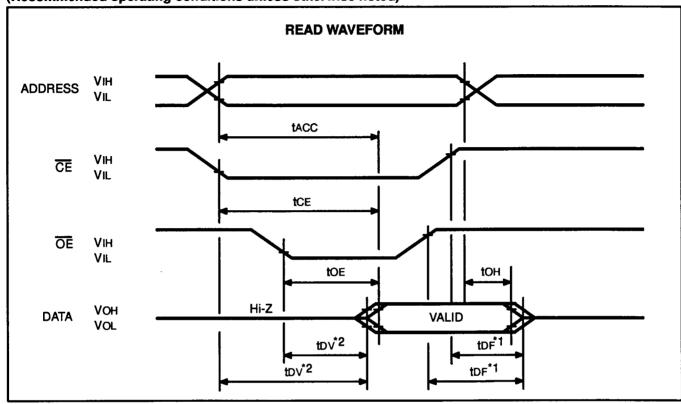

(Recommended operating conditions unless otherwise noted)

| Parameter                             | Symbol |     | 24001-12-X<br>lues | MBM27C<br>Val | Unit |    |

|---------------------------------------|--------|-----|--------------------|---------------|------|----|

|                                       |        | Min | Max                | Min           | Max  |    |

| Address Access Time                   | tACC   |     | 120                |               | 150  | ns |

| CE to Output Delay Time               | tCE    |     | 120                |               | 150  | ns |

| OE to Output Delay Time               | tOE    |     | 70                 |               | 70   | ns |

| CE or OE to Output Float Delay (Note) | tDF    |     | 60                 |               | 60   | ns |

| Address to Output Hold Time           | tOH    | 0   |                    | 0             |      | ns |

| CE or OE to Output Active             | tD∨    | 0   |                    | 0             |      | ns |

NOTE: Output Float is defined as the point where data is no longer driven.

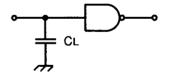

## **AC TEST CONDITIONS**

Fig. 2 —AC TEST CONDITIONS(INCLUDING PROGRAMMING)

Input Pulse Levels:

0.45V to 2.4V

Input Rise/Fall Times:

≤20ns

Input Reference Levels:

0.8V to 2.0V

Output Reference Levels:

0.8V to 2.0V

Output Load:

1 TTL gate and CL = 100pF

# **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted)

NOTE:\*1: tDF is specified by either of  $\overline{CE}$  or  $\overline{OE}$  changing to high earlier.

\*2: tDV is specified by either of  $\overline{CE}$  or  $\overline{OE}$  changing to low later.

## PROGRAMMING / ERASING INFORMATION

#### **PROGRAMMING**

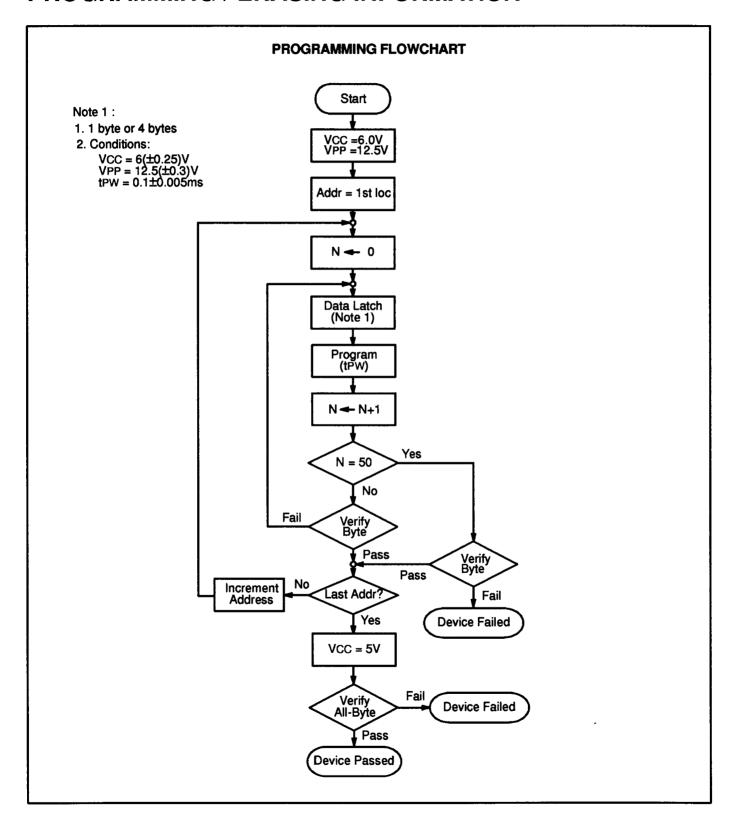

Single-Byte Programming. When +12.5V( $\pm 0.3$ ) volts are applied to Vpp, +6( $\pm 0.25$ ) volts are to VCC and  $\overline{CE}$ ,  $\overline{OE}$  =VIH (TTL), theprogramming mode is initiated. Address is selected for programmingby address pins A0 to A18 and input data is applied to output pins D0 to D7. When both address and data are stable, a 0.1-millisecond negative pulse is applied to the  $\overline{OE}$  pin. Upon verification of written data should be applied to complete the programming of one byte. Refer to the PRO-GRAMMING FLOWCHART that follows for step-by-step programming procedures.

Four-Byte Programming. Compared to the Single-byte programming , the Four-byte programming method reduces programming time by about 75%. Voltages applied to VPP and VCC are the same as in the Single-byte programming; however some logic levels differ (refer to "Four Byte Programming" in the truth table ). In conjunction with  $\overline{OE}$  pin, address pins Ao and A1 are used to latch four bytes of data. When both address and data are stable, a 0.1-millisecond negative pulse is applied to the  $\overline{OE}$  pin. Upon verification of written data should be applied to complete the programming of four-byte.

#### Caution

In program mode (VPP=12.5V( $\pm 0.3$ )), a continue us TTL low-level Voltage should not be applied to the  $\overline{CE}$ . Also a 0.1-microfarad capacitor must be connected between VPP and ground to prevent excessive voltage transient. Neglecting

either of these precautions may cause device failure.

Electronic Signature/Programming Algorithm. When MBM27C4001 is shipped from the factory, all memory cells (4,194,304 bits) are set to the High state (logic 1). During the programming procedure, affected bit cells are set to the Low (logic 0) state.

Manufacturer and device codes are electronically stored in each device. The Electronic Signature Code List is shown in the table preceding the ELECTRICAL CHARACTERISTICS.

#### **ERASING**

In order to clear all memory cells of programmed contents, the MBM27C4001 must be exposed to an ultraviolet light source. To completely erase the memory (restore all cells to a logic 1 state), a dosage of 10Wsec/cm2 is required. The required exposure can be obtained by using a UV-lamp with a wavelength of 2537 Angstroms and with an intensity of 12mW/cm<sup>2</sup>. Remove all filters from the lamp and clean the transparent lid of the MBM27C4001 with a non-abrasive cleaner. Hold the MBM27C4001 approximately one inch from the light source for 15 to 20 minutes. (Note. The MBM27C4001 and other similar devices can be erased by light sources with longer wavelengths: however, the erasing time is much greater. Nonetheless, exposure to fluorescents or sunlight will severely degrade and eventually erase the memory. When used in a lighted environment, it is recommended that the transparent window be covered with an opaque label.)

#### **ELECTRONIC SIGNATURE CODE LIST**

| Definition  | A0  | A1 to A8 | <b>A</b> 9 | A10 to A18 | ŌΕ  | ĈĒ  | D0 | D1 | D2 | Dз | D4 | D5 | D6 | D7 | HEX |

|-------------|-----|----------|------------|------------|-----|-----|----|----|----|----|----|----|----|----|-----|

| Manufacture | VIL | VIL      | 12(±0.5)V  | VIL        | VIL | ۷L  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | #04 |

| Device      | VIH | VIL      | 12(±0.5)V  | VIL        | VIL | VIL | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | #F4 |

# PROGRAMMING / ERASING INFORMATION (Cont'd)

#### DC CHARACTERISTICS

$(TA = 25 \text{ °C} \pm 5 \text{ °C}, VCC = 6V \pm 0.25V, VPP = 12.5V \pm 0.3V)$

| Barrana tau                      | Combal. | Candillana         |      | Values |          |      |

|----------------------------------|---------|--------------------|------|--------|----------|------|

| Parameter                        | Symbol  | Conditions         | Min  | Тур    | Max      | Unit |

| Input Leakage Current            | iLi     | VIN = 6.25V/0V     |      |        | 10       | μΑ   |

| VPP Supply Current (Single-Byte) | lPP1    | CE = VIL, OE = VIH |      |        | 30       | mA   |

| VPP Supply Current (Four-Byte)   | IPP2    | CE = VIL, OE = VIH |      |        | 50       | mA   |

| VPP Supply Current (Inhibit)     | IPP3    | CE = VIH, OE = VIH |      |        | 5        | mA   |

| VPP Supply Current (Verify)      | IPP4    | CE = VIL, OE = VIL |      |        | 5        | mA   |

| VCC Supply Current               | ICC     |                    |      |        | 50       | mA   |

| Input Low Level                  | VIL     |                    | -0.1 |        | 0.8      | ٧    |

| Input High Level                 | VIH     |                    | 2.0  |        | VCC +0.3 | ٧    |

| Output Low Level                 | VOL     | IOL = 2.1mA        |      |        | 0.45     | ٧    |

| Output High Level                | Vон     | IOH = -400μA       | 2.4  |        |          | ٧    |

NOTE: \*1 VCC must be applied either coincidentally or before VPP and removed either coincidentally or after VPP.

#### **AC CHARACTERISTICS**

$(TA = 25 \text{ °C} \pm 5 \text{ °C}, V_{CC} = 6V \pm 0.25V, V_{PP} = 12.5V \pm 0.3V)$

| Parameter                     | Simbol |     | Values |     | Unit  |

|-------------------------------|--------|-----|--------|-----|-------|

| Par ameter                    | Symbol | Min | Тур    | Max | ] """ |

| Address Setup Time            | tas    | 0.5 |        |     | μs    |

| Address Hold Time             | tah    | 0.5 |        |     | μs    |

| Data Setup Time               | tDS    | 0.5 |        |     | μs    |

| Data Hold Time                | tDH    | 0.5 |        |     | μs    |

| OE Hold Time("L")             | tOEL   | 0.5 |        |     | μs    |

| OE Hold Time("H")             | tOEH   | 0.5 |        |     | μs    |

| Hold Time Before Programming  | thbp   | 2   |        |     | μs    |

| Programming Pulse Width       | tPW    | 95  | 100    | 105 | μs    |

| Over Programming Pulse Number | N      | 1   |        | 50  | times |

<sup>\*2</sup> VPP must not be 13.5volts or more including overshoot. Permanent device damage may occuer if the device is taken out or put into socket remaining VPP=12.5 volts. Also, during CE=VIL, OE=VIH, VPP must not be switched from VCC to VPP volts or vice versa.

## AC CHARACTERISTICS(Cont'd)

| Parameter                      | Symbol | Values |     |     |      |

|--------------------------------|--------|--------|-----|-----|------|

|                                |        | Min    | Тур | Max | Unit |

| Hold Time After Programming    | tHAP   | 2      |     |     | μs   |

| CE Setup Time                  | tCES   | 2      |     |     | μs   |

| OE Setup Time                  | tOES   | 2      |     |     | μs   |

| Input Data Floating Setup Time | tDFS   | 1      |     |     | μs   |

| Address Access Time at Verify  | tACV   |        |     | 500 | ns   |

| OE to Output Float             | tDFV   |        |     | 150 | ns   |

| Hold Time After Verify         | tAHV   | 0      |     |     | μs   |

| VPP Setup Time                 | tVPS   | 20     |     |     | μs   |

| VPP Hold Time                  | tvcs   | 20     |     |     | μs   |

Note 1: When verify fails, return to data latch.

## **PROGRAMMING / ERASING INFORMATION**

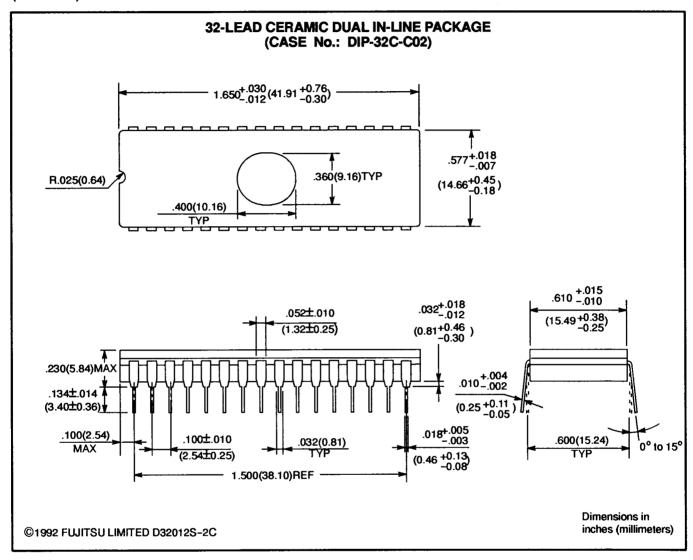

## PACKAGE DIMENSIONS

(Suffix: Z)

#### All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Complete Information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The Information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.