# 2107C FAMILY 4096-BIT DYNAMIC RAM

|                             | 2107C-1 | 2107C-2 | 2107C | 2107C-4 |

|-----------------------------|---------|---------|-------|---------|

| Access Time (ns)            | 150     | 200     | 250   | 300     |

| Read, Write Cycle (ns)      | 380     | 400     | 430   | 470     |

| RMW Cycle (ns)              | 450     | 500     | 550   | 590     |

| Max I <sub>DD AV</sub> (mA) | 35      | 33      | 30    | 30      |

- Direct Replacement for Industry Standard 22-Pin 4K RAMs

- Low Operating Power

- Low Standby Power

- Only One High Voltage Input Signal-Chip Enable

- 150 ns Access Time

- ±10% Tolerance on all Power Supplies

- Output is Three-State and TTL Compatible

- TTL Compatible All Address, Data, Write Enable, Chip Select Inputs

- Refresh Period 2 ms

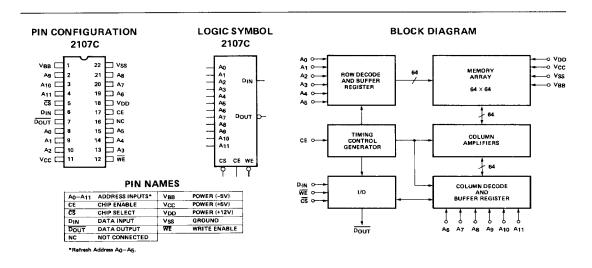

The Intel® 2107C is a 4096-word by 1-bit dynamic n-channel MOS RAM. It was designed for memory applications where very low cost and large bit storage are important design objectives. A new unique dynamic storage cell provides high speed and wide operating margins. The 2107C uses dynamic circuitry which reduces the standby power dissipation.

Reading information from the memory is non-destructive. Refreshing is most easily accomplished by performing one read cycle on each of the 64 row addresses. Each row address must be refreshed every two milliseconds. The memory is refreshed whether Chip Select is a logic one or a logic zero.

The 2107C is fabricated with n-channel silicon gate technology. This technology allows the design and production of high performance, easy to use MOS circuits and provides a higher functional density on a monolithic chip than other MOS technologies. The 2107C is a replacement for the 2107A, 2107B and other industry standard 22-pin 4K RAMs.

# **Absolute Maximum Ratings\***

| Temperature Under Bias                                                                  |       |

|-----------------------------------------------------------------------------------------|-------|

| Storage Temperature                                                                     |       |

| Voltage on any Pin Relative to V <sub>BB</sub> (V <sub>SS</sub> - V <sub>BB</sub> ≥4.5) |       |

| Power Dissipation                                                                       | 1.00W |

#### \*COMMENT:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. and Operating Characteristics

$T_A = 0^{\circ} C$  to  $70^{\circ} C$ ,  $V_{DD} = +12V \pm 10\%$ ,  $V_{CC} = +5V \pm 10\%$ ,  $V_{BB}^{[1]} = -5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

| Symbol Parameter     | _                                                       |                    | Limits              |                    | Unit | Conditions                                                                               |

|----------------------|---------------------------------------------------------|--------------------|---------------------|--------------------|------|------------------------------------------------------------------------------------------|

|                      | Parameter                                               | Min.               | Typ. <sup>[2]</sup> | Max.               | Unit | Conditions                                                                               |

| LI                   | Input Load Current (all inputs except CE)               |                    |                     | 10                 | μΑ   | V <sub>IN</sub> = 0V to V <sub>IH MAX</sub><br>CE = V <sub>ILC</sub> or V <sub>IHC</sub> |

| LC                   | Input Load Current, CE                                  |                    |                     | 2                  | μΑ   | V <sub>IN</sub> = 0V to V <sub>IHC MAX</sub>                                             |

| LO                   | Output Leakage Current for high impedance state         |                    |                     | 10                 | μΑ   | $CE = V_{1LC} \text{ or } \overline{CS} = V_{1H}$<br>$V_0 = 0V \text{ to } 5.5V$         |

| DD1 <sup>[3]</sup>   | V <sub>DD</sub> Supply Current — standby <sup>[3]</sup> |                    | 20                  | 200                | μΑ   | CE = -1V to +0.6V                                                                        |

| DD AV                |                                                         |                    | 24                  | 35                 | mA   | 2107C-1, t <sub>CYC</sub> = 380                                                          |

|                      | Average V <sub>DD</sub> Current — operating             |                    | 22                  | 33                 | mA   | 2107C-2, t <sub>CYC</sub> = 400                                                          |

|                      |                                                         |                    | 20                  | 30                 | mA   | 2107C, t <sub>CYC</sub> = 430                                                            |

|                      |                                                         |                    | 20                  | 30                 | mA   | 2107C-4, t <sub>CYC</sub> = 470                                                          |

| CC1 <sup>[3,4]</sup> | V <sub>CC</sub> Supply Current — standby                |                    |                     | 10                 | μΑ   | CE = V <sub>ILC</sub> or $\overline{CS}$ = V <sub>IH</sub>                               |

| BB1                  | V <sub>BB</sub> Supply Current — standby                |                    | 5                   | 50                 | μΑ   | CE = -1V to +0.6V                                                                        |

| BB AV                | Average V <sub>BB</sub> Current – operating             |                    | 100                 | 400                | μΑ   | Min. cycle time, Min. t <sub>CE</sub>                                                    |

| /IL                  | Input Low Voltage                                       | -1.0               |                     | 0.8                | ٧    |                                                                                          |

| /ін                  | Input High Voltage                                      | 2.4                |                     | V <sub>CC</sub> +1 | ٧    |                                                                                          |

| /ILC                 | CE Input Low Voltage                                    | -1.0               |                     | +1.0               | ٧    |                                                                                          |

| /інс                 | CE Input High Voltage                                   | V <sub>DD</sub> -1 |                     | V <sub>DD</sub> +1 | ٧    |                                                                                          |

| /oL                  | Output Low Voltage                                      | 0.0                |                     | 0.40               | ٧    | I <sub>OL</sub> = 3.2 mA                                                                 |

| /он                  | Output High Voltage                                     | 2.4                |                     | Vcc                | ٧    | I <sub>OH</sub> = -2.0 mA                                                                |

#### NOTES:

- 1. The only requirement for the sequence of applying voltage to the device is that V<sub>DD</sub>, V<sub>CC</sub>, and V<sub>SS</sub> should never be 0.3V or more negative than V<sub>DD</sub>.

- 2. Typical values are for T<sub>A</sub> = 25°C and nominal power supply voltages.

- 3. The IDD and ICC currents flow to VSS.

- 4. During CE on V<sub>CC</sub> supply current is dependent on output loading. V<sub>CC</sub> is connected to output buffer only.

# A.C. Characteristics (1)

$T_{A} = 0^{\circ} C \text{ to } 70^{\circ} C, \ \ V_{DD} = 12 V \ \pm 10\%, \ \ V_{CC} = 5 V \ \pm 10\%, \ \ V_{BB} = -5 V \ \pm 10\%, \ \ V_{SS} = 0 V, \ \text{unless otherwise noted}.$

#### READ, WRITE, AND READ MODIFY/WRITE CYCLE

| Symbol Parameter | 2107C-1                       |      | 2107C-2 |      | 2107C |      | 2107C-4 |      |      |       |      |

|------------------|-------------------------------|------|---------|------|-------|------|---------|------|------|-------|------|

|                  | Parameter                     | Min. | Max     | Min. | Max.  | Min. | Max.    | Min. | Max. | Units | Note |

| tREF             | Time Between Refresh          |      | 2       |      | 2     |      | 2       |      | 2    | ms    |      |

| tAC              | Address to CE Set-Up Time     | 0    |         | 0    |       | 0    |         | 0    |      | ns    | 2    |

| tan              | Address Hold Time             | 50   |         | 50   |       | 100  |         | 100  |      | ns    | _    |

| tcc              | CE Off Time                   | 130  |         | 130  |       | 130  |         | 130  |      | ns    |      |

| tŢ               | CE Transition Time            |      | 40      |      | 40    |      | 40      |      | 40   | ns    |      |

| t <sub>CD</sub>  | CE Off to Output Disable Time | 30   |         | 30   |       | 30   |         | 30   |      | ns    | 3    |

#### READ CYCLE

| Symbol Parameter | D                        | 2107C-1 |      | 2107C-2 |      | 2107C |      | 2107C-4 |       |      |   |

|------------------|--------------------------|---------|------|---------|------|-------|------|---------|-------|------|---|

|                  | Min.                     | Max.    | Min. | Max.    | Min. | Max.  | Min. | Max.    | Units | Note |   |

| t <sub>CY</sub>  | Cycle Time               | 380     |      | 400     |      | 430   |      | 470     |       | ns   | 3 |

| t <sub>CE</sub>  | CE On Time               | 210     | 4000 | 230     | 4000 | 260   | 4000 | 300     | 4000  | ns   |   |

| tco              | CE Output Delay          |         | 130  |         | 180  |       | 230  |         | 280   | ns   | 4 |

| tACC             | Address to Output Access |         | 150  |         | 200  |       | 250  |         | 300   | ns   | 5 |

| t <sub>WL</sub>  | CE to WE                 | 0       |      | 0       |      | 0     |      | 0       |       | ns   |   |

| twc              | WE to CE On              | 0       |      | 0       |      | 0     |      | 0       |       | ns   |   |

#### WRITE CYCLE

| Symbol          | _                            | 210  | 2107C-1 |      | 2107C-2 |      | 2107C |      | 2107C-4 |       | l    |

|-----------------|------------------------------|------|---------|------|---------|------|-------|------|---------|-------|------|

|                 | Parameter                    | Min. | Max.    | Min. | Max.    | Min. | Max.  | Min. | Max.    | Units | Note |

| t <sub>CY</sub> | Cycle Time                   | 380  |         | 400  |         | 430  |       | 470  |         | ns    | 3    |

| t <sub>CE</sub> | CE On Time                   | 210  | 4000    | 230  | 4000    | 260  | 4000  | 300  | 4000    | ns    |      |

| tw              | WE to CE Off                 | 125  |         | 125  |         | 125  | İ     | 175  |         | ns    |      |

| tcw             | CE to WE                     | 150  |         | 150  |         | 150  |       | 200  |         | ns    |      |

| t <sub>DW</sub> | D <sub>IN</sub> to WE Set-Up | 0    |         | 0    |         | 0    |       | 0    |         | ns    | 6    |

| t <sub>DH</sub> | D <sub>IN</sub> Hold Time    | 0    |         | 0    |         | 0    |       | 0    |         | ns    |      |

| t <sub>WP</sub> | WE Pulse Width               | 50   |         | 50   |         | 50   |       | 100  |         | ns    |      |

| t <sub>WD</sub> | WE to Output Disable Time    | 15   |         | 15   |         | 15   |       | 15   |         |       |      |

# Capacitance [7] TA = 25°C

| Symbol           | Test                                     | 1    | ic and<br>Package | Unit | Conditions                        |  |  |  |

|------------------|------------------------------------------|------|-------------------|------|-----------------------------------|--|--|--|

|                  |                                          | Тур. | Max.              |      |                                   |  |  |  |

| C <sub>AD</sub>  | Address Capacitance, CS, D <sub>IN</sub> | 5    | 7                 | рF   | V <sub>IN</sub> = V <sub>SS</sub> |  |  |  |

| C <sub>CE</sub>  | CE Capacitance                           | 10   | 15                | рF   | V <sub>IN</sub> = V <sub>SS</sub> |  |  |  |

| C <sub>OUT</sub> | Data Output Capacitance                  | 5    | 7                 | рF   | V <sub>OUT</sub> = 0V             |  |  |  |

| CWE              | WE Capacitance                           | 6    | 8                 | pF   | V <sub>IN</sub> = V <sub>SS</sub> |  |  |  |

#### NOTES:

- After the application of supply voltages or after extended periods of operation without CE, the device must perform a minimum of one initialization cycle (any valid memory cycle or refresh cycle) prior to normal operation.

- 2. tAC is measured from end of address transition.

- 3. t<sub>T</sub> = 20 ns.

- 4.  $C_{LOAD}$  = 50 pF, Load = One TTL Gate, Ref = 2.0V.

- 5. tACC = tAC + tCO + 1tT.

- If WE is low before CE goes high then D<sub>IN</sub> must be valid when CE goes high.

- 7. Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:

- $C = \frac{I \triangle t}{\triangle V}$  with the current equal to a constant 20 mA.

3-30

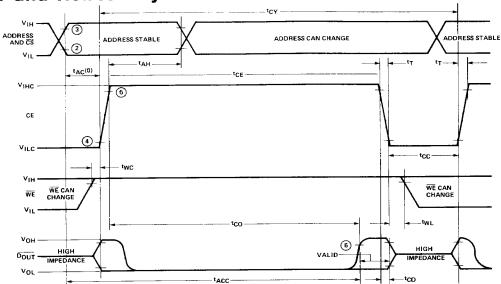

# Read and Refresh Cycle [1]

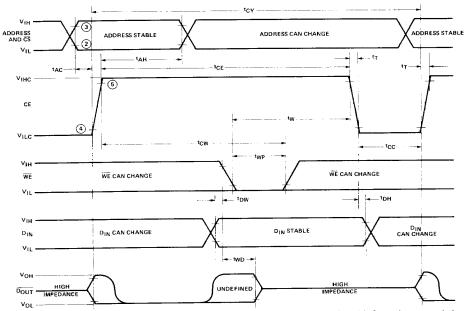

## **Write Cycle**

- NOTES: 1. For Refresh cycle, row and column addresses must be stable before tAC and remain stable for entire tAH period.

- 2. VIL MAX is the reference level for measuring timing of the addresses, CS, WE, and DIN.

- 3.  $V_{IN}$  MIN is the reference level for measuring timing of the addresses,  $\overline{CS}$ ,  $\overline{WE}$ , and  $D_{IN}$ .

- 4. VSS +2.0V is the reference level for measuring timing of CE.

- 5. VDD -2V is the reference level for measuring timing of CE.

- 6.  $V_{SS}$  +2.0V is the reference level for measuring the timing of  $\overline{D_{OUT}}$ .

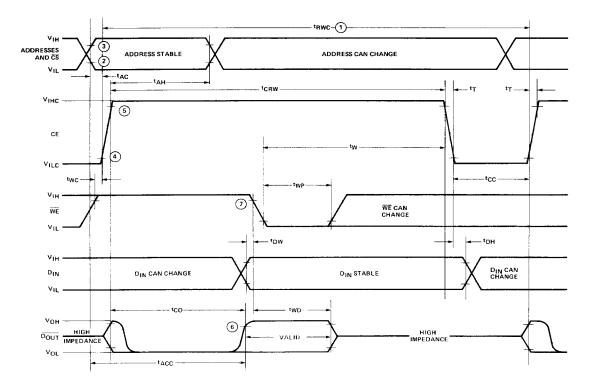

## **Read Modify Write Cycle**

| Symbol Parameter |                               | 2107C-1 |      | 2107C-2 |      | 2107C |      | 2107C-4 |      | Units | Note |

|------------------|-------------------------------|---------|------|---------|------|-------|------|---------|------|-------|------|

|                  | Parameter                     | Min.    | Max. | Min.    | Max. | Min.  | Max. | Min.    | Max. |       |      |

| tRWC             | Read Modify Write (RMW) Cycle | 450     |      | 500     |      | 550   |      | 590     |      | ns    | 1    |

| tcRW             | CE Width During RMW           | 280     | 4000 | 330     | 4000 | 380   | 4000 | 420     | 4000 | ns    |      |

| twc              | WE to CE On                   | 0       |      | 0       |      | 0     |      | 0       |      | ns    |      |

| tw               | WE to CE Off                  | 125     |      | 125     |      | 125   |      | 175     |      | ns    |      |

| twp              | WE Pulse Width                | 50      |      | 50      |      | 50    |      | 100     |      | ns    |      |

| t <sub>DW</sub>  | D <sub>IN</sub> to WE Setup   | 0       |      | 0       |      | 0     |      | 0       |      | ns    |      |

| t <sub>DH</sub>  | D <sub>IN</sub> Hold Time     | 0       |      | 0       |      | 0     |      | 0       |      | ns    |      |

| tco              | CE to Output Delay            |         | 130  |         | 180  |       | 230  |         | 280  | ns    |      |

| tACC             | Access Time                   |         | 150  |         | 200  |       | 250  |         | 300  | ns    |      |

| twD              | WE to Output Disable Time     | 15      |      | 15      |      | 15    |      | 15      |      | ns    |      |

- NOTES: 1.  $t_T$  of 20 ns.

- 2. VIL MAX is the reference level for measuring timing of the addresses,  $\overline{\text{CS}}$ ,  $\overline{\text{WE}}$ , and DIN.

- 3. VIH MIN is the reference level for measuring timing of the addresses, CS, WE, and DIN.

- 4.  $V_{SS}$  +2.0V is the reference level for measuring timing of CE.

- 5. V<sub>DD</sub> -2V is the reference level for measuring timing of CE.

- 6. VSS +2.0V is the reference level for measuring the timing of DOUT. CLOAD = 50 pF. Load = One TTL Gate.

- 7. WE must be at VIH until end of tco.