## RAM

## MM5260 1024-bit fully decoded dynamic random access memory

#### general description

The MM5260 fully decoded dynamic 1024 word x 1-bit word read/write random access memory is a monolithic MOS integrated circuit using silicon gate low threshold technology to achieve bipolar compatibility on all I/O lines except the precharge and read/write lines. This provides an efficient approach to memory design using this systems oriented device. The MM5260 is used for main memory applications where large bit storage and improved operating performance are important. A TRI-STATE™ output is utilized to allow wired "OR" capability and common I/O data busing in memory applications.

#### features

■ Fast access time

350 ns

Fast cycle time

450 ns read cycle min 600 ns write cycle min

Low overhead circuit count

Fully decoded

Systems-oriented design

Bipolar compatib (address lines, ch

enable data I/ Common data I/O li TRI-STATE Outp

2.0

static char

+5V, -12 400 m

Refresh cycle

Easy memory expansion Chip enal Device protection All I/O lines ha protection again

Standard power supplies

Low power dissipation

■ Small package size 16 pin dual-in-line packa

#### applications

- High speed mainframe memory

- Mass memory storage

#### typical application

#### Main Mamory Module Storing 4096 16-Bit Words

## absolute maximum ratings

All Input or Output Voltages with

Respect to Most Positive Supply Voltage V<sub>SS</sub>

Power Dissipation

Operating Temperature Range Storage Temperature Range Lead Temperature (Soldering, 10 sec) +0.3V to 20V 600 mW

-25 C to +70 C 65 C to +150 C

300 C

## dc operating characteristics

$T_A$  within operating temperature range,  $V_{SS}$  = +5V ±5%,  $V_{DD}$  = -12V ±5%, unless otherwise noted.

| PARAMETER                                                                               | CONDITIONS                   | MIN                   | TYP | MAX                   | UNITS |

|-----------------------------------------------------------------------------------------|------------------------------|-----------------------|-----|-----------------------|-------|

| Input Voltage (Address input, chip enable and data input)                               |                              |                       |     | İ                     |       |

| Logic "0" (V <sub>IH</sub> )<br>Logic "1" (V <sub>IL</sub> )                            |                              | V <sub>S5</sub> - 2.0 |     | V <sub>SS</sub> - 4.0 | v     |

| Input voltage (Precharge and Read/Write)                                                |                              |                       |     |                       |       |

| Logic "0" (V <sub>IH</sub> )                                                            | }                            | V <sub>SS</sub> - 1.5 |     |                       | V     |

| Logic "1" (ViL)                                                                         |                              |                       |     | V <sub>SS</sub> - 15  | V     |

| Output Voltage<br>Data Output                                                           |                              |                       |     |                       |       |

| Logic "0" (VoH)                                                                         | IL + 200 µA Source           | 2 4                   |     |                       | \ \   |

| Logic "1" (VoL)                                                                         | I <sub>t</sub> · 1.6 mA Sink |                       |     | 0.4                   | V     |

| Average Supply Current (I <sub>DD</sub> ) t cycle = 450 ns and t <sub>pc</sub> = 300 ns |                              |                       | 20  |                       | mA    |

## ac operating characteristics

$T_A$  within operating temperature range,  $V_{SS}$  = +5V  $\pm$ 5V%,  $V_{DD}$  =  $\pm$ 12V  $\pm$ 5%, unless otherwise noted.

| Read Cycle (T <sub>RC</sub> )                    |                                   | ns<br>ns |  |

|--------------------------------------------------|-----------------------------------|----------|--|

| 600                                              |                                   | ns       |  |

|                                                  |                                   | 1        |  |

|                                                  | (600 + T <sub>D</sub> See Note 1) |          |  |

| Access Time (T <sub>A</sub> )                    |                                   | ns       |  |

| Address to Chip Enable (T <sub>AC</sub> ) Note 2 | 50                                | ns       |  |

| Address to Precharge Delay (TAPL) Note 2         | 50                                | ns       |  |

| Address to Write Pulse Delay (TAWO)              |                                   | ns       |  |

| Write Pulse Width (Twp)                          | 1                                 | ns       |  |

| Precharge Off Time (Tpp)                         | ł                                 | ns       |  |

| Read Write to Precharge Delay (Twine) 50         | 1                                 | ns       |  |

| Refresh Interval (TREE)                          | 2                                 | ıms      |  |

| Address to Precharge Trailing Edge (TAPY) 350    |                                   | ns       |  |

## capacitance characteristics

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0                                                                                                                             |                                                                                                                                                      | _       |                |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|

|                                                        | Chip Enable Capacitance (C <sub>CE</sub> ) Precharge Capacitance (C <sub>PC</sub> ) Read/Write Capacitance (C <sub>RW</sub> ) | V <sub>IN</sub> * V <sub>SS</sub> V <sub>IN</sub> * V <sub>SS</sub> V <sub>IN</sub> = V <sub>SS</sub> V <sub>IN</sub> = V <sub>SS</sub> di AC Ground | 5<br>25 | pF<br>pF<br>pF |

Note 1: T<sub>D</sub> = Output data to input data delay in read-modify write cycle.

Note 2: Characteristic max limits to achieve  $T_A$  specifications. An increase in these times will cause  $T_A$  to increase directly.

## **Channel Matching**

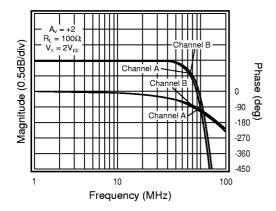

Channel matching and crosstalk efficiency are largely dependent on board layout. The layout of National's dual amplifier evaluation boards are optimized to produce maximum channel matching and isolation. Typical channel matching for the CLC417 is shown in Figure 3.

Figure 3: Channel Matching

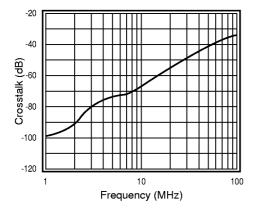

The CLC417's channel-to-channel isolation is better than 70dB for input frequencies of 4MHz. Input referred crosstalk vs. frequency is illustrated in Figure 4.

Figure 4: Input Referred Crosstalk vs. Frequency

## **Driving Cables and Capacitive Loads**

When driving cables, double termination is used to prevent reflections. For capacitive load applications, a small series resistor at the output of the CLC417 will improve stability. The  $R_s$  vs. Capacitive Load plot, in the Typical Performance section, gives the recommended series resistance value for optimum flatness at various capacitive loads.

## **Power Dissipation**

The power dissipation of an amplifier can be described in two conditions:

- Quiescent Power Dissipation -P<sub>O</sub> (No Load Condition)

- Total Power Dissipation P<sub>T</sub> (with Load Condition)

The following steps can be taken to determine the power consumption for each CLC417 amplifier:

- 1. Determine the quiescent power

- P<sub>Q</sub> = (V<sub>CC</sub> V<sub>EE</sub>) · I<sub>CC</sub>

2. Determine the RMS power at the output stage

P<sub>O</sub> = (V<sub>CC</sub> V<sub>load</sub>) (I<sub>load</sub>), where V<sub>load</sub> and I<sub>load</sub>

are the RMS voltage and current across the external load.

- 3. Determine the total RMS power  $P_T = P_O + P_O$

Add the total RMS powers for both channels to determine the power dissipated by the dual.

The maximum power that the package can dissipate at a given temperature is illustrated in the *Power Derating* curves in the *Typical Performance* section. The power derating curve for any package can be derived by utilizing the following equation:

$$P = \frac{(175^{\circ} - Tamb)}{\theta_{.1\Delta}}$$

where: T<sub>amb</sub> = Ambient temperature (°C) θ<sub>JA</sub> = Thermal resistance, from junction to ambient, for a given package (°C/W)

## **Layout Considerations**

A proper printed circuit layout is essential for achieving high frequency performance. National provides evaluation boards for the CLC417 (CLC730038 - DIP, CLC730036 - SOIC) and suggests their use as a guide for high frequency layout and as an aid for device testing and characterization.

Supply bypassing is required for best performance. The bypass capacitors provide a low impedance return current path at the supply pins. They also provide high frequency filtering on the power supply traces. Other layout factors play a major role in high frequency performance. The following are recommended as a basis for high frequency layout:

- 1. Include 6.8μF tantalum and 0.1μF ceramic capacitors on both supplies.

- 2. Place the  $6.8\mu F$  capacitors within 0.75 inches of the power pins.

- 3. Place the  $0.1\mu F$  capacitors less than 0.1 inches from the power pins.

- 4. Remove the ground plane near the input and output pins to reduce parasitic capacitance.

- 5. Minimize all trace lengths to reduce series inductances.

Additional information is included in the evaluation board literature.

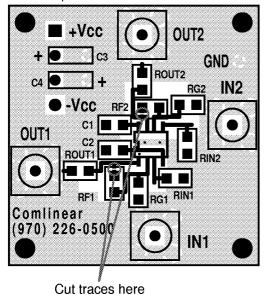

## **Special Evaluation Board Considerations**

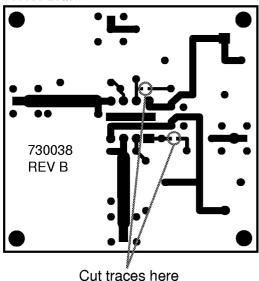

To optimize off-isolation of the CLC417, cut the  $R_{\rm f}$  trace on both the 730038 and 730036 evaluation boards. This cut minimizes capacitive feedthrough between the input and output. Figure 5 indicates the alterations recommended to improve off-isolation.

730036 Top

730038 Bottom

Figure 5: Optional Evaluation Board Alterations

## **SPICE Models**

SPICE models provide a means to evaluate amplifier designs. Free SPICE models are available for National's monolithic amplifiers that:

- Support Berkeley SPICE 2G and its many derivatives

- Reproduce typical DC, AC, Transient, and Noise performance

- Support room temperature simulations

The *readme* file that accompanies the diskette lists released models, and provides a list of modeled parameters. The application note OA-18, Simulation SPICE Models for National's Op Amps, contains schematics and a reproduction of the *readme* file.

# **Applications Circuits**

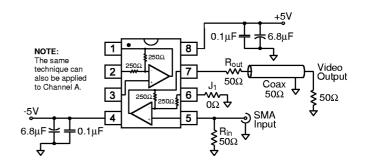

## **Video Cable Driver**

The CLC417 was designed to produce exceptional video performance at all three closed-loop gains. A typical cable driving configuration is shown in Figure 6. In this example, the amplifier is configured with a gain of 2.

Figure 6: Typical Cable Driver

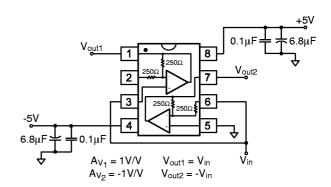

## Single to Differential Line Driver

The topology in Figure 7 accomplishes a single-ended to differential conversion with no external components. With this configuration, the value of Vin is limited to the common mode input range of the CLC417.

Figure 7: Single to Differential Line Driver