# TMS 2147H JL, NL, FPL FAST 4096-WORD BY 1-BIT STATIC RAM

FEBRUARY 1981 - REVISED MAY 1982

- 4096 X 1 Organization

- Single +5 V Supply (± 10% Tolerance)

- High-Density 300-mil (7.62 mm) Packages

- Fully Static Operation (No Clocks, No Refresh, No Timing Strobe)

- Fast . . . 4 Performance Ranges:

|             | ACCESS<br>TIME<br>(MAX) | READ OR WRITE<br>CYCLE<br>(MIN) |

|-------------|-------------------------|---------------------------------|

| TMS 2147H-3 | 35 ns                   | 35 ns                           |

| TMS 2147H-4 | 45 ns                   | 45 ns                           |

| TMS 2147H-5 | 55 ns                   | 55 ns                           |

| TMS 2147H-7 | 70 ns                   | 70 ns                           |

- Inputs and Outputs TTL Compatible

- Common I/O Capability

- 3-State Outputs and Chip Enable Control for OR-Tie Capability

- Automatic Chip Enable/Power Down Operation

- Reliable SMOS (Scaled-MOS) N-Channel Technology

- Direct Performance Upgrade for Industry Standard 2147

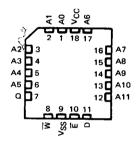

#### TMS 2147H 18-PIN PLASTIC AND CERAMIC DUAL-IN-LINE PACKAGES (TOP VIEW)

### 18-PIN PLASTIC CHIP CARRIER PACKAGE (TOP VIEW)

### PIN NAMES

| A0-A11 | Addresses              |

|--------|------------------------|

| D      | Data In                |

| Q      | Data Out               |

| Ē      | Chip Enable/Power Down |

| Vcc    | +5 V Supply            |

| VSS    | Ground                 |

| W      | Write Enable           |

### description

These high-speed static random-access memories are organized as 4096 words of 1 bit. Static design results in reduced overhead costs by elimination of refresh-clocking circuitry and by simplification of timing requirements. Automatic chip enable/power down allows devices to be placed in the reduced-power mode whenever deselected,

All inputs and outputs are fully compatible with Series 74, 74S or 74LS TTL. No pull-up resistors are required. These 4K static RAM series are manufactured using TI's reliable state-of-the-art SMOS (scaled MOS) N-channel silicon-gate technology to optimize the cost/performance relationship.

The TMS 2147H is offered in 18-pin dual-in-line plastic (NL suffix) and ceramic (JL suffix) packages designed for insertion in mounting-hole rows on 300-mil (7.62 mm) centers. An 18-pin plastic chip carrier (FP suffix) is also available. The series is guaranteed for operation from 0°C to 70°C.

# TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

582

# TMS 2147H JL, NL, FPL FAST 4096-WORD BY 1-BIT STATIC RAM

### operation

### addresses (A0-A11)

The 12 address inputs select one of the 4096 storage locations in the RAM. The address inputs must be stable for the duration of a write cycle. The address inputs can be driven directly from standard Series 54/74 TTL with no externa pull-up resistors.

#### chip enable/power down (E)

The chip enable/power down terminal, which can be driven directly by standard TTL circuits, affects the data-in and data-out terminals and the internal functioning of the chip itself. Whenever the chip enable/power down is low (enabled), the device is operational, input and output terminals are enabled, and data can be read or written. When the chip enable/power down terminal is high (disabled), the device is deselected and put into a reduced-power standby mode. Data is retained during standby.

### write-enable (W)

The read or write mode is selected through the write-enable terminal. A logic high selects the read mode; a logic low selects the write mode.  $\overline{W}$  must be high when changing addresses to prevent erroneously writing data into a memory location. The  $\overline{W}$  input can be driven directly from standard TTL circuits.

#### data-in (D)

Data can be written into a selected device when the write-enable input is low. The data-in terminal can be driver directly from standard TTL circuits.

#### data-out (O)

The three-state output buffer provides direct TTL compatibility. The output is in the high-impedance state when chip enable/power down (Ē) is high or whenever a write operation is being performed, facilitating device operation in common I/O systems. Data-out is the same polarity as data-in.

### FUNCTION TABLE

| INP | UTS | OUTPUT   |            |

|-----|-----|----------|------------|

| Ē   | w   | Q        | MODE       |

| н   | ×   | Hi-Z     | POWER DOWN |

| L   | L   | Hi-Z     | WRITE      |

| L   | Н   | DATA OUT | READ       |

Texas Instruments

INCORPORATED

POST OFFICE BOX 225012 . DALLAS TEXAS 75265

92

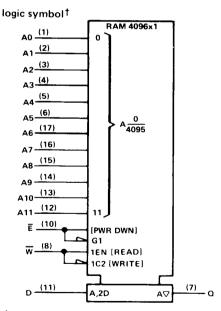

<sup>†</sup> This symbol is in accordance with IEEE Std 91/ANSI Y32.14 and recent decisions by IEEE and IEC. See explanation on page 289.

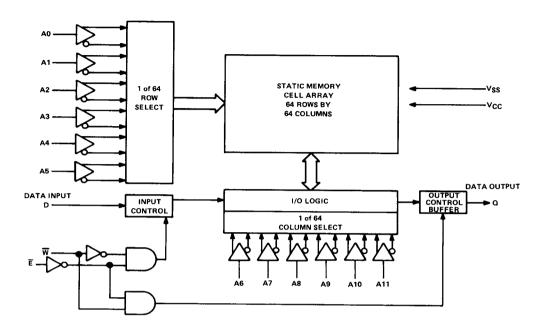

### functional block diagram

## absolute maximum ratings over operating ambient temperature<sup>†</sup> range (unless otherwise noted)<sup>‡</sup>

| Supply voltage, V <sub>CC</sub> (see Note 1) | -1.5 V to 7 V |

|----------------------------------------------|---------------|

| Input voltage (any input) (see Note 1)       | -1.5 V to 7 V |

| Continuous power dissipation                 | 1 W           |

| Operating ambient temperature range          | 0°C to 70°C   |

| Storage temperature range                    |               |

### recommended operating conditions

| PARAMETER                                                   | MIN NOM | MAX | UNIT |

|-------------------------------------------------------------|---------|-----|------|

| Supply voltage, VCC                                         | 4.5 5   | 5.5 | V    |

| Supply voltage, V <sub>SS</sub>                             | 0       |     | v    |

| High-level input voltage, V <sub>IH</sub>                   | 2       | 6   | V    |

| Low-level input voltage, V <sub>IL</sub>                    | -1 §    | 0.8 | V    |

| Operating ambient temperature <sup>†</sup> , T <sub>A</sub> | 0       | 70  | °C   |

<sup>&</sup>lt;sup>†</sup>The ambient temperature conditions assume air moving perpendicular to the longitudinal axis and parallel to the seating plane of the device at a velocity of 400 ft/min (122 m/min) with the device under test soldered to a 4 X 6 X 0.062-inch (102 X 152 X 1.6-mm) double-sided 2-ounce copper-clad circuit board (plating thickness 0.07 mm).

### TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

<sup>\*</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. The algebraic convention, where the more negative limit is designated as minimum, is used in this data sheet for logic voltage levels only.

# TMS 2147H JL, NL, FPL FAST 4096-WORD BY 1-BIT STATIC RAM

## electrical characteristics over recommended operating ambient temperature<sup>†</sup> range (unless otherwise noted)

|                  | PARAMETER                                     | Т                                                                      | EST CONDITIONS                 |                         | MIN | TYP‡ | MAX | UNIT |

|------------------|-----------------------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------------|-----|------|-----|------|

| Voн              | High-level output voltage                     | I <sub>OH</sub> = -4 mA,                                               | V <sub>CC</sub> = 4.5 V        |                         | 2.4 |      |     | V    |

| VOL              | Low-level output voltage                      | I <sub>OL</sub> = 8 mA,                                                | V <sub>CC</sub> = 4.5 V        |                         |     |      | 0.4 | V    |

| I <sub>I</sub>   | Input current                                 | V <sub>I</sub> ≈ 0 V to 5.5 V                                          |                                |                         |     |      | 10  | μA   |

| loz              | Off-state output current                      | E at 2 V,                                                              | V <sub>O</sub> = 0 V to 4.5 V, | V <sub>CC</sub> = 5.5 V |     |      | ±50 | μА   |

| 1004             | Standby supply current                        | Ē at V <sub>IH</sub>                                                   |                                |                         |     |      |     |      |

| <sup>1</sup> CC1 | from V <sub>CC</sub>                          | CatalH                                                                 |                                |                         |     | 18   | 30  | mA   |

|                  |                                               | $\vec{E}$ at $V_{IL}$<br>$I_O = 0$ mA, $T_A = 0^\circ$<br>(worst case) | С                              |                         |     | 90   | 120 | mA   |

| ICC2             | Operating supply current from V <sub>CC</sub> | Ē at V <sub>IL</sub><br>I <sub>O</sub> = 0 mA<br>T <sub>A</sub> = 70°C |                                |                         |     |      | 100 | mA   |

| IPO              | Peak power-on current<br>(see Note 2)         | V <sub>CC</sub> = GND to V <sub>CC</sub>                               |                                |                         |     |      | 70  | mA   |

| Ci               | Input capacitance                             | V <sub>I</sub> = 0 V,                                                  | f = 1 MHz                      |                         |     |      | 5   | pF   |

| СО               | Output capacitance                            | V <sub>O</sub> = 0 V,                                                  | f = 1 MHz                      |                         |     |      | 6   | ρF   |

### ac test conditions

| Input pulse levels                           |         |          | <br> |      | G    | ina | ) to 3 | ١, |

|----------------------------------------------|---------|----------|------|------|------|------|------|------|------|------|------|-----|--------|----|

| Input rise and fall times                    |         | <b>.</b> | <br> |     | . 5    | n  |

| Input timing reference levels                |         |          | <br> |     | 1.5    | 1  |

| Output timing reference level (2147H-3) .    |         |          | <br> |     | 1.5    | ١, |

| Output timing reference high level (2147H-4, | , -5, - | 7)       | <br> |     | . 2    | ١. |

| Output timing reference, low level (2147H-4, | , -5, - | 7)       | <br> |     | 0.8    | ١  |

| Output loading                               |         |          |      |      |      |      |      |      |      |      | S    |     | Figur  | ٠. |

### timing requirements over recommended supply voltage range and operating ambient temperature<sup>†</sup> range

|                    | DADAMETED                          | TMS 2147H | 3 TMS 2 | 147H-4 | TMS 2 | 147H-5 | TMS 2 |     |      |

|--------------------|------------------------------------|-----------|---------|--------|-------|--------|-------|-----|------|

|                    | PARAMETER                          | MIN MA    | X MIN   | MAX    | MIN   | MAX    | MIN   | MAX | UNIT |

| tc(rd)             | Read cycle time                    | 35        | 45      |        | 55    |        | 70    |     | ns   |

| tc(wr)             | Write cycle time                   | 35        | 45      |        | 55    |        | 70    |     | ns   |

| tw(W)              | Write pulse width                  | 20        | 25      |        | 25    |        | 40    |     | ns   |

| t <sub>su(A)</sub> | Address setup time                 | 0         | 0       |        | 0     |        | 0     |     | ns   |

| t <sub>su(E)</sub> | Chip enable setup time             | 35        | 45      |        | 45    |        | 55    |     | ns   |

| t <sub>su(D)</sub> | Data setup time                    | 20        | 25      |        | 25    |        | 30    |     | ns   |

| th(D)              | Data hold time                     | 10        | 10      |        | 10    |        | 10    |     | ns   |

| th(A)              | Address hold time                  | 0         | 0       |        | 10    |        | 15    |     | ns   |

| †AVWH              | Address valid to write enable high | 35        | 45      |        | 45    |        | 55    |     | ns   |

<sup>†</sup> The ambient temperature conditions assume air moving at a velocity of 400 ft/min (122 m/min).

NOTE 2: IPO exceeds I<sub>CC1</sub> maximum during power on. A pull-up resistor to V<sub>CC</sub> on the E input is required to keep the device deselected otherwise, power-on current approaches I<sub>CC2</sub>.

### TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

94

<sup>&</sup>lt;sup>‡</sup> All typical values are at  $V_{CC} = 5$ ,  $T_A = 25^{\circ}C$ .

# switching characteristics over recommended supply voltage range and operating ambient temperature<sup>†</sup> range

|                     | PARAMETER                                          | TEST                                               | TMS 2 | 147H-3 | 3 TMS 2147H-4 |     | TMS 2 | TMS 2147H-5 |     | 147H-7 |      |  |

|---------------------|----------------------------------------------------|----------------------------------------------------|-------|--------|---------------|-----|-------|-------------|-----|--------|------|--|

|                     |                                                    | CONDITIONS                                         | MIN   | MAX    | MIN           | MAX | MIN   | MAX         | MIN | MAX    | UNIT |  |

| ta(A)               | Access time from address                           |                                                    |       | 35     |               | 45  |       | 55          |     | 70     | ns   |  |

| ta(E)               | Access time from chip enable                       |                                                    |       | 35     |               | 45  |       | 55          |     | 70     |      |  |

| * ***               | Output data valid after                            |                                                    |       |        |               |     |       | - 33        |     | - 70   | ns   |  |

| tv(A)               | address change                                     |                                                    | 5     |        | 5             |     | 5     |             | 5   |        | ns   |  |

| tdis(W)             | Output disable time from write enable <sup>‡</sup> |                                                    |       | 20     |               | 25  |       | 25          |     | 35     | ns   |  |

| t <sub>en</sub> (W) | Output enable time from write enable <sup>‡</sup>  | R <sub>L</sub> = 510 Ω,<br>C <sub>L</sub> = 30 pF, | 0     |        | 0             |     | 0     |             | 0   |        | ns   |  |

| <sup>t</sup> dis(E) | Output disable time from chip enable <sup>‡</sup>  | See Figure 1                                       |       | 30     |               | 30  |       | 30          |     | 40     | ns   |  |

| ten(E)              | Output enable time from chip enable <sup>‡</sup>   |                                                    | 5     |        | 5             |     | 10    |             | 10  |        | ns   |  |

| <sup>t</sup> pwrdn  | Power down time from<br>chip select                |                                                    |       | 20     |               | 20  |       | 20          |     | 30     | ns   |  |

$<sup>^{\</sup>dagger}$  The ambient temperature conditions assume air moving at a velocity of 400 ft/mln (122 m/min).

## PARAMETER MEASUREMENT INFORMATION

FIGURE 1 - LOAD CIRCUIT

TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

$<sup>^{\</sup>ddagger}$ Transition is measured  $\pm500$  mV from steady state voltage with specified loading in Figure 1.

# TMS 2147H JL, NL, FPL FAST 4096-WORD BY 1-BIT STATIC RAM

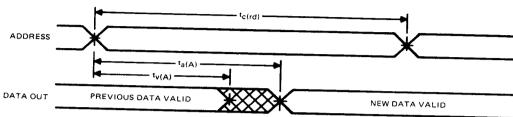

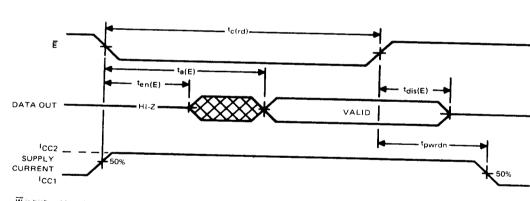

### read cycle timing

from address

W is high, E is low.

### from chip select

$\overline{W}$  is high, address is valid prior to or simultaneously with the high-to-low transition of  $\overline{E}_s$

# TEXAS INSTRUMENTS

INCORPORATED

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

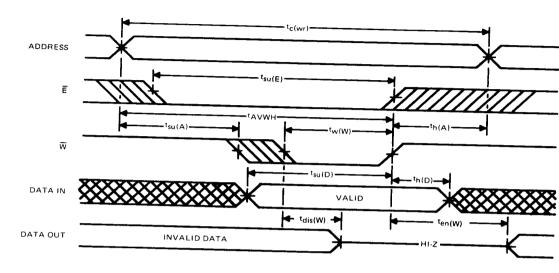

# write cycle timing controlled by write enable†

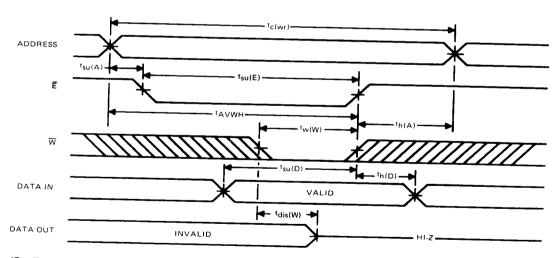

## controlled by chip enable†

$^\dagger$ E or  $\overline{W}$  must be high during address transitions. NOTE: If  $\overline{E}$  goes high simultaneously with  $\overline{W}$  going high, the output remains in the high-impedance state.

# Texas Instruments

INCORPORATED

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

This Material Copyrighted By Its Respective Manufacturer

# TMS 2147H JL, NL, FPL FAST 4096-WORD BY 1-BIT STATIC RAM

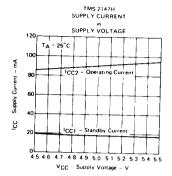

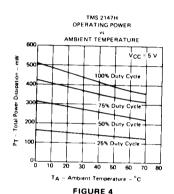

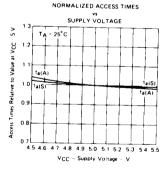

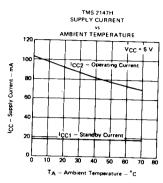

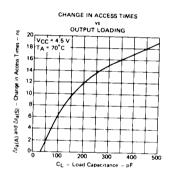

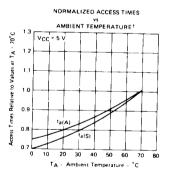

## TYPICAL CHARACTERISTICS

FIGURE 2

FIGURE 6

FIGURE 3

FIGURE 5

FIGURE 7

INCORPORATED

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

$^\dagger$  The ambient temperature conditions assume air moving at a velocity of 400 feet per minute,

TEXAS INSTRUMENTS