# FUJITSU MICROELECTRONICS

# MOS 4096-BIT STATIC RANDOM ACCESS MEMORY

MBM2147H-70 MBM2147H-55 MBM2147H-45 MBM2147H-35

#### DESCRIPTION

The Fujitsu MBM2147H is a 4096 words by 1 bit static random access memory fabricated using N-channel silicon gate MOS technology. Separate input/output pins are provided. All devices are fully compatabile with TTL logic families in all respects: inputs, outputs and the use of a

single +5V DC supply. For ease of use, chip select (CS) permits the selection of an individual package when outputs are ORtied, and automatically powers down the MBM2147H. All devices offer the advantage of low power dissipation, low cost and high performance.

# **FEATURES**

- Organization: 4096 words X 1 bit

- Static operation, no clocks or refresh required

- Fast Access Time:

MBM2147H-70: 70 ns Max MBM2147H-55: 55 ns Max MBM2147H-45: 45 ns Max MBM2147H-35: 35 ns Max

- Single +5V DC supply voltage

- TTL compatible input/output

- 3-state output with OR-tie capability

- Chip select with automatic power down

- Standard 18 pin DIP package

- Pin compatible with Intel 2147/2147H

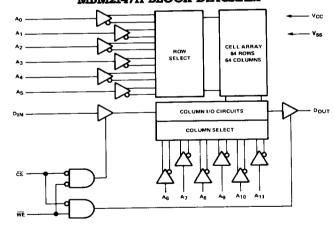

# MBM2147H BLOCK DIAGRAM

#### TRUTH TABLE

| cs | WE | MODE         | OUTPUT | POWER   |  |  |

|----|----|--------------|--------|---------|--|--|

| Н  | Х  | NOT SELECTED | HIGH Z | STANDBY |  |  |

| L  | L  | WRITE        | HIGH Z | ACTIVE  |  |  |

| L  | н  | READ         | Dout   | ACTIVE  |  |  |

CERDIP PACKAGE DIP-18C-C01

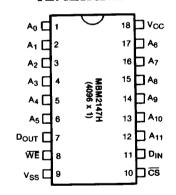

### PIN ASSIGNMENT

This device contains circultry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

# ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                             | Symbol                                               | Value       | Unit |  |

|----------------------------------------------------|------------------------------------------------------|-------------|------|--|

| Voltage On Any Pin with respect to V <sub>SS</sub> | V <sub>IN</sub> , V <sub>OUT</sub> , V <sub>CC</sub> | -3.5 to +7  | ٧    |  |

| DC Output Current                                  | lo                                                   | 20          | mA   |  |

| Temperature Under Bias                             | T <sub>A</sub>                                       | -10 to +85  | °C   |  |

| Storage Temperature                                | T <sub>stg</sub>                                     | -65 to +150 | °C   |  |

| Power Dissipation                                  | P <sub>D</sub>                                       | 1.2         | W    |  |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet.

# RECOMMENDED OPERATING CONDITIONS

(Referenced to V<sub>SS</sub>)

| Parameter          | Symbol          | Min  | Тур | Max | Unit | Ambient<br>Temperature |

|--------------------|-----------------|------|-----|-----|------|------------------------|

| Supply Voltage     | Vcc             | 4.5  | 5.0 | 5.5 | V    |                        |

| Input Low Voltage  | VIL             | -3.0 | _   | 8.0 | V    | 0°C to +70°C           |

| Input High Voltage | V <sub>IH</sub> | 2.0  | _   | 6.0 | V    |                        |

#### CAPACITANCE

$(T_A = 25 \,^{\circ}C; f = 1MHz)$

| Parameter                                  | Symbol           | Тур | Max | Unit |

|--------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> = 0V)   | CIN              | _   | 5   | pF   |

| Output Capacitance (V <sub>OUT</sub> = 0V) | C <sub>OUT</sub> | _   | 6   | pF   |

#### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                   |                                        | Symbol          | Min  | Max | Unit |

|---------------------------------------------------------------------------------------------|----------------------------------------|-----------------|------|-----|------|

| Input Leakage Current (VIN = VSS to                                                         | V <sub>CC</sub> ,V <sub>CC</sub> = Max | լլյ             | _    | 10  | μΑ   |

| Output Leakage Current (CS = V <sub>IH</sub> , to V <sub>CC</sub> , V <sub>CC</sub> = Max.) |                                        | lLO             |      | 50  | μА   |

| Power Supply Current (V <sub>CC</sub> = Max,                                                | H-70                                   |                 | _    | 160 | mA.  |

| CS = V <sub>IL</sub> , I <sub>OUT</sub> = 0mA)                                              | H-55/H-45/H-35                         | lcc             |      | 180 | 1110 |

| Output Low Voltage (IOI = 8mA)                                                              | V <sub>OL</sub>                        | _               | 0.4  | V   |      |

| Output High Voltage (IOH = -4mA)                                                            |                                        | V <sub>OH</sub> | 2.4  | 1   | V    |

| Standby Current, (V <sub>CC</sub> = Max,                                                    | H-70                                   |                 | _    | 20  | mA   |

| CS = V <sub>IH</sub> , I <sub>OUT</sub> = 0mA)                                              | H-55/H-45/H-35                         | ls <b>B</b>     |      | 30  |      |

| Peak Power-On Current (V <sub>CC</sub> = V <sub>SS</sub>                                    | H-70                                   |                 |      | 50  | mA.  |

| to V <sub>CC</sub> Min, CS = Lower of V <sub>CC</sub> or V <sub>IN</sub> Min.)              | H-55/H-45/H-35                         | lpo             |      | 70  | mA.  |

| Output Short Circuit Current                                                                | los                                    | -200            | +200 | mA  |      |

# AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

|                                                     |                   | MBM2147H-70 |          | MBM2147H-55 |     | MBM2147H-45 |          | MBM2147H-35 |     |      |

|-----------------------------------------------------|-------------------|-------------|----------|-------------|-----|-------------|----------|-------------|-----|------|

| Parameter<br>Note                                   | Symbol            | Min         | Max      | Min         | Max | Min         | Max      | Min         | Max | Unit |

| Read Cycle Time                                     | t <sub>RC</sub>   | 70          | <b>—</b> | 55          | _   | 45          | _        | 35          |     | ns   |

| Address Access Time                                 | tAA               | 1 -         | 70       | _           | 55  |             | 45       |             | 35  | ns   |

| Chip Select Access Time 1                           | t <sub>ACS1</sub> | T           | 70       |             | 55  | _           | 45       | <u> </u>    | 35  | ns   |

| Chip Select Access Time 2                           | t <sub>ACS2</sub> | T           | 80       |             | 65  |             | 45       |             | 35  | ns   |

| Previous Read Data Valid<br>After Change of Address | tон               | 5           |          | 5           |     | 5           | <u> </u> | 5           |     | ns   |

| Chip Select to Power Up                             | tpU               | 0           | T -      | 0           | _   | 0           |          | 0           | L   | ns   |

| Chip Select to Output Active                        | tLZ               | 10          | T -      | 10          | Τ — | 5           |          | 5           |     | ns   |

| Chip Select to Output<br>Three-Stated               | t <sub>HZ</sub>   | 0           | 40       | 0           | 40  | 0           | 30       | 0           | 30  | ns   |

| Chip Select to Power Down                           | t <sub>PD</sub>   | T -         | 30       | _           | 30  | l —         | 20       |             | 20  | ns   |

MBM2147H

Notes: 1) Chip deselected for greater than 55 ns prior to selection.

2) Chip deselected for a finite time that is less than 55 ns prior to selection. (If the deselect time is 0 ns, the chip is by definition selected and access occurs according to Read Cycle: Address Changing.)

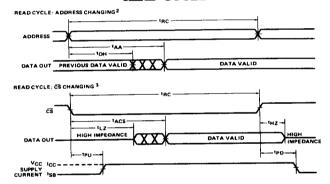

# READ CYCLE<sup>1</sup>

Netes: 1) WE is high for read cycle.

2) Device is continuously selected,  $\overline{CS} = V_{IL}$ 3) Addresses valid prior to or coincident with  $\overline{CS}$  low transition.

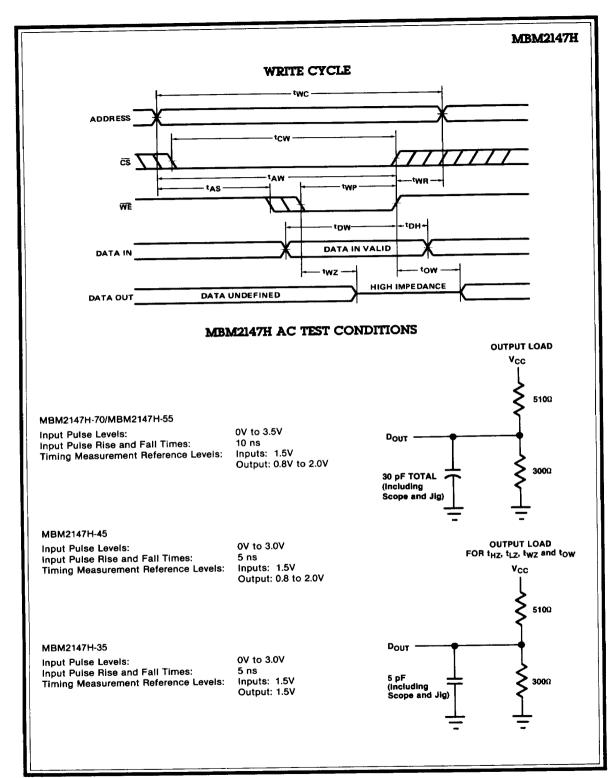

# WRITE CYCLE

|                                        |                 |     | MBM2147H-70 |     | MBM2147H-55 |     | MBM2147H-45 |     | MBM2147H-35 |      |

|----------------------------------------|-----------------|-----|-------------|-----|-------------|-----|-------------|-----|-------------|------|

| Parameter                              | Symbol          | Min | Max         | Min | Max         | Min | Max         | Min | Max         | Unit |

| Write Cycle Time                       | twc             | 70  |             | 55  | <u> </u>    | 45  |             | 35  |             | ns   |

| Address Valid to End of Write          | t <sub>AW</sub> | 55  | T —         | 45  | _           | 45  |             | 35  |             | ns   |

| Chip Select to End of Write            | tcw             | 55  | _           | 45  | _           | 45  |             | 35  |             | ns   |

| Data Valid to End of Write             | t <sub>DW</sub> | 30  | T —         | 25  | _           | 25  | _           | 20  | ]           | ns   |

| Data Hold Time                         | tDH             | 10  | T -         | 10  | _           | 10  | _           | 10  | _           | ns   |

| Write Pulse Width                      | twp             | 40  |             | 35  | _           | 25  | _           | 20  |             | ns   |

| Write Recovery Time                    | twe             | 15  | T           | 10  | _           | 0   |             | 0   |             | ns   |

| Address Setup Time                     | tas             | 0   | I —         | 0   | _           | 0   | <del></del> | 0   |             | ns   |

| Output Active From End of Write        | tow             | 0   |             | 0   |             | 0   |             | 0   | _           | ns   |

| Write Enabled to Output<br>Three-State | t <sub>WZ</sub> | 0   | 35          | 0   | 30          | 0   | 25          | 0   | 20          | ns   |

#### **MBM2147H**

#### DESCRIPTION

The MBM2147 family from Fujitsu are high performance parts. They are designed for high speed and low system power requirements.

The high speed is obtained by advanced NMOS processing. The low system power requirements are achieved by the use of the MBM2147's chip select (active low). The MBM2147 automatically enters standby (drawing only ISB) whenever the chip select is high.

Upon activation of chip select ( $\overline{CS} = LOW$ ) the MBM2147 automatically powers up and draws I<sub>CC</sub>.

This automatic power up/down is an extremely useful feature. However, care must be used as proper decoupling and PC board layout is required to minimize power line glitches.

PC board layout with proper V<sub>CC</sub> decoupling will minimize power line glitches.

Input and data bus lines are an additional area of concern. Unless bus lines are properly designed and terminated, cross coupling, cross talk and reflections can occur. Of particular importance is the undershoot on address lines. Once again, careful attention to good PC board layout and proper termination techniques will yield a well designed and reliable memory system.

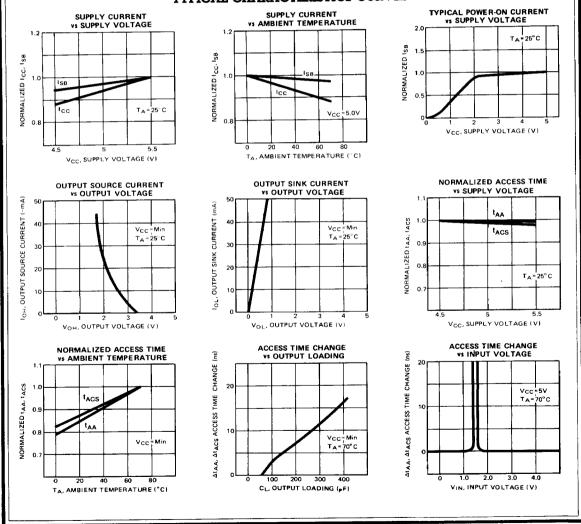

# TYPICAL CHARACTERISTICS CURVES