# 262,144 x 8 HIGH-SPEED CMOS EPROM

PRELIMINARY JULY 1996

## **FEATURES**

- Fast read access time: 70 ns

- Industrial and commercial temperature ranges available

- ±10% power supply tolerance

- JEDEC-approved pinout

- Standard 32-pin PDIP, PLCC, and TSOP packages

## **DESCRIPTION**

The *ISSI* IS27C020 is an ultra-high-speed 2 megabit (256K-word by 8-bit) Ultraviolet Erasable CMOS Programmable Read-Only Memory. This superior random access capability results from a focused high-speed design.

The device is ideal for use with the faster processors. Designers may take full advantage of high-speed digital signal processors and microprocessors by allowing code to be executed at full speed directly out of EPROM. Typical applications include laser printers, switching networks, graphics, workstations, high-speed modems, and digital signal processing.

The IS27C020 uses ISSI's write programming algorithm which allows the entire chip to be programmed in typically less than 30 seconds.

This product is available in One-Time Programmable (OTP) PDIP, PLCC, and TSOP packages over commercial and industrial temperature ranges.

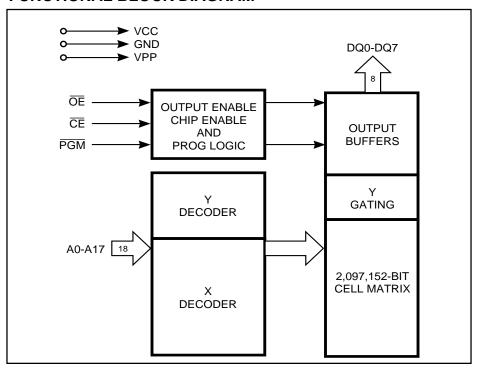

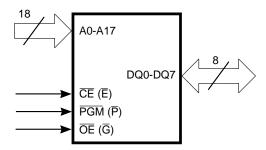

## **FUNCTIONAL BLOCK DIAGRAM**

This document contains preliminary data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1996, Integrated Silicon Solution, Inc.

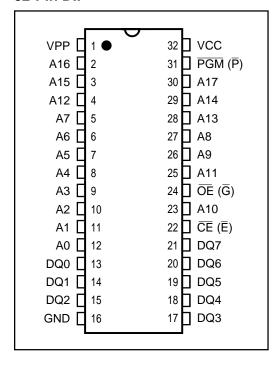

# PIN CONFIGURATIONS 32-Pin DIP

## **PIN DESCRIPTIONS**

| A0-A17  | Address Inputs         |  |

|---------|------------------------|--|

| CE (E)  | Chip Enable Input      |  |

| DQ0-DQ7 | Data Inputs/Outputs    |  |

| ŌĒ (G)  | Output Enable Input    |  |

| PGM (P) | Program Enable Input   |  |

| Vcc     | Power Supply Voltage   |  |

| VPP     | Program Supply Voltage |  |

| GND     | Ground                 |  |

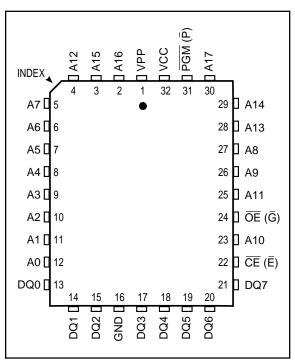

## 32-Pin PLCC

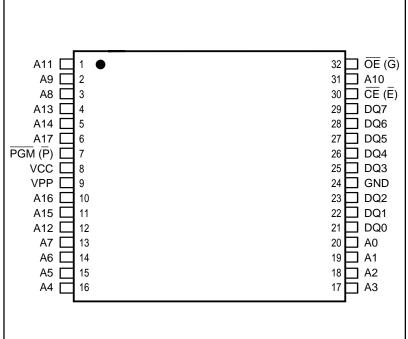

#### 32-Pin TSOP

## **FUNCTIONAL DESCRIPTION**

## Erasing the IS27C020

In order to clear all locations of their programmed contents, it is necessary to expose the IS27C020 to an ultraviolet light source. A dosage of 30W - sec/cm² is required to completely erase the IS27C020. This dosage can be obtained by exposure to an ultraviolet lamp-wavelength of 2537 Angstroms (Å)—with intensity of 12,000  $\mu$ W/cm² for 30 to 40 minutes. The IS27C020 should be directly under and about one inch from the source and all filters should be removed from the UV light source prior to erasure.

It is important to note that the IS27C020, and similar devices, will erase with light sources having wavelengths shorter than 4000Å. The exposure to fluorescent light and sunlight will eventually erase the IS27C020 and exposure to them should be prevented to realize maximum system reliability. If used in such an environment, the package window should be covered by an opaque label or substance.

#### Programming the IS27C020

Upon delivery, or after each erasure, the IS27C020 has 2,097,152 bits in the "ONE", or HIGH state. "ZEROs" are loaded into the IS27C020 through the procedure of programming.

The programming mode is entered when  $12.75 \pm 0.25 \text{V}$  is applied to the VPP pin, Vcc = 6.25 V,  $\overline{\text{CE}}$  and  $\overline{\text{PGM}}$  is at V<sub>IL</sub>, and  $\overline{\text{OE}}$  is at V<sub>IH</sub>. For programming, the data to be programmed is applied eight bits in parallel to the data output pins.

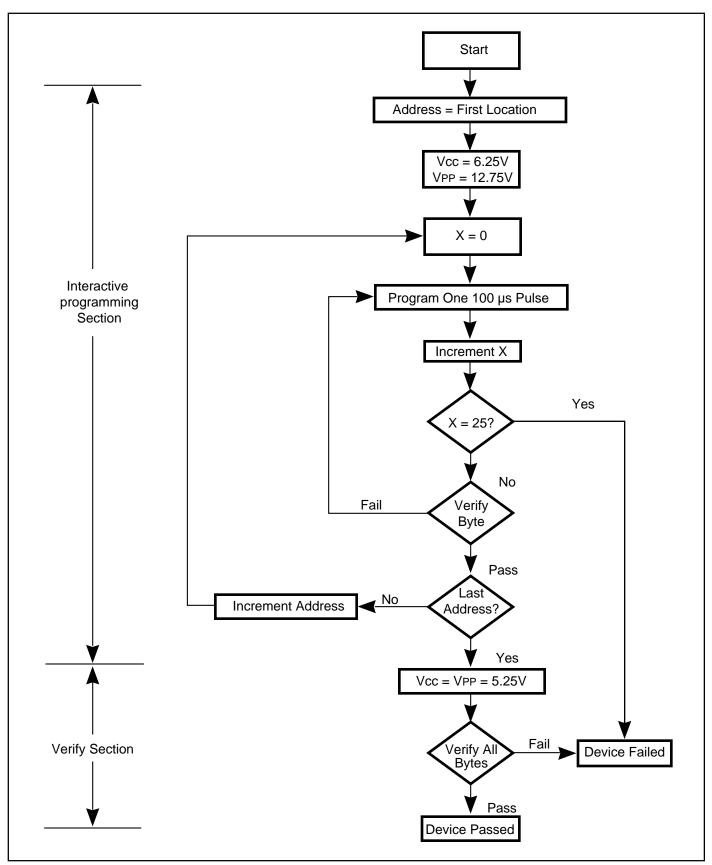

The write programming algorithm reduces programming time by using 100  $\mu s$  programming pulses followed by a byte verification to determine whether the byte has been successfully programmed. If the data does not verify, an additional pulse is applied for a maximum of 25 pulses. This process is repeated while sequencing through each address of the EPROM.

The write programming algorithm programs and verifies at Vcc = 6.25V and Vpp = 12.75V. After the final address is completed, all byte are compared to the original data with Vcc = 5.25V.

#### **Program Inhibit**

Programming of multiple IS27C020s in parallel with different data is also easily accomplished. Except for  $\overline{\text{CE}}$ , all like inputs of the parallel IS27C020 may be common. A TTL low-level program pulse applied to an IS27C020  $\overline{\text{CE}}$  input with VPP = 12.75  $\pm$  0.25V,  $\overline{\text{PGM}}$  LOW and  $\overline{\text{OE}}$  HIGH will program that IS27C020. A high-level  $\overline{\text{CE}}$  input inhibits the other IS27C020 from being programmed.

#### **Program Verify**

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify should be performed with  $\overline{OE}$  and  $\overline{CE}$  at V<sub>IL</sub>,  $\overline{PGM}$  at V<sub>IH</sub>, and V<sub>PP</sub> between 12.5V and 13.0V.

#### **Auto Select Mode**

The auto select mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25°C  $\pm$ 5°C ambient temperature range that is required when programming the IS27C020.

To activate this mode, the programming equipment must force  $12.0\pm0.5V$  on address line A9 of the IS27C020. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from VIL to VIH. All other address lines must be held at VIL during auto select mode.

Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code, and byte 1 (A0 =  $V_{IH}$ ), the device identifier code. For the IS27C020, these two identifier bytes are given in the Mode Select table. All identifiers manufacturer and device codes will possess odd parity, with the MSB (DQ7) defined as the parity bit.

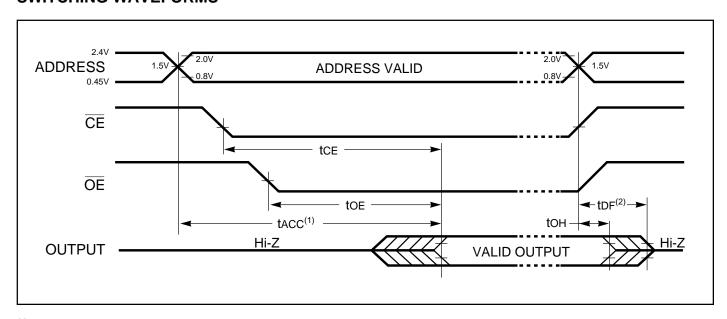

#### **Read Mode**

The IS27C020 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable  $(\overline{CE})$  is the power control and should be used for device selection. Assuming that addresses are stable, address access time (tacc) is equal to the delay from  $\overline{CE}$  to output (tce). Output Enable  $(\overline{OE})$  is the output control and should be used to get data to the output pins, independent of device selection. Data is available at the outputs toe after the falling edge of  $\overline{OE}$  assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least tacc – toe.

## **Standby Mode**

The IS27C020 has a standby mode which reduces the maximum Vcc active current. It is placed in standby mode when  $\overline{\text{CE}}$  is at Vih. The amount of current drawn in standby mode depends on the frequency and the number of address pins switching. The IS27C020 is specified with 50% of the address lines toggling at 10 MHz. A reduction of the frequency or quantity of address lines toggling will significantly reduce the actual standby current.

#### **Output OR-Tieing**

To accommodate multiple memory connections, a twoline control function is provided to allow for:

- 1. Low memory power dissipation, and

- Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device-selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### **System Applications**

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device at a minimum, a 0.1  $\mu F$  ceramic capacitor (high-frequency, low inherent inductance) should be used on each device between Vcc and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on EPROM arrays, a 4.7  $\mu F$  bulk electrolytic capacitor should be used between Vcc and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

## TRUTH TABLE(1,2)

| Mode                                         | CE    | ŌĒ  | PGM | A0  | A9 | VPP | Outputs      |

|----------------------------------------------|-------|-----|-----|-----|----|-----|--------------|

| Read                                         | VIL   | VIL | Х   | Х   | Х  | Vcc | <b>D</b> оит |

| Output Disable                               | VIL   | ViH | Х   | Х   | Х  | Vcc | Hi-Z         |

| Standby                                      | ViH   | Х   | Х   | Х   | Х  | Vcc | Hi-Z         |

| Program                                      | VIL   | Vih | VIL | Х   | Х  | Vpp | Din          |

| Program Verify                               | VIL   | VIL | Vih | Х   | Х  | Vpp | <b>D</b> оит |

| Program Inhibit                              | ViH   | Х   | Х   | Х   | Х  | Vpp | Hi-Z         |

| Auto Select <sup>(3)</sup> Manufacturer Code | e VIL | VIL | Х   | VIL | Vн | Vcc | D5H          |

| Device Code                                  | e Vil | VIL | Χ   | Vін | Vн | Vcc | 97H          |

#### Notes:

- 1.  $V_H = 12.0V \pm 0.5V$ .

- 2. X = Either VIH or VIL.

- 3. A1-A8 = A10-A17 = VIL.

- 4. See DC Programming Characteristics for VPP voltage during programming.

## LOGIC SYMBOL

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Parameter                              | Value                         | Unit |

|--------|----------------------------------------|-------------------------------|------|

| VTERM  | Terminal Voltage with Respect to GND   |                               |      |

|        | All pins except A9 and VPP             | $-0.6$ to Vcc + $0.5^{(2)}$   | V    |

|        | VPP                                    | $Vcc - 0.3$ to $13.5^{(2,3)}$ | V    |

|        | A9                                     | -0.6 to 13.5 <sup>(2,3)</sup> | V    |

|        | Vcc                                    | $-0.6$ to $7.0^{(2)}$         | V    |

| TA     | Ambient Temperature with Power Applied | -65 to +125                   | °C   |

| Тѕтс   | Storage Temperature (OTP)              | -65 to +125                   | °C   |

| Тѕтс   | Storage Temperature (All others)       | -65 to +150                   | °C   |

#### Notes:

- Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the

device. This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect reliability.

- 2. Minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods less than 10 ns. Maximum DC voltage on output pins is Vcc + 0.5V which may overshoot to Vcc + 2.0V for periods less than 10 ns.

- 3. Maximum DC voltage on A9 or VPP may overshoot to +13.5V for periods less than 10 ns.

## **OPERATING RANGE**

| Range         | Ambient Temperature | Vcc      |

|---------------|---------------------|----------|

| Commercial    | 0°C to +70°C        | 5V ± 10% |

| Industrial(1) | –40°C to +85°C      | 5V ± 10% |

#### Note:

1. Operating ranges define those limits between which the functionally of the device is guaranteed.

## DC ELECTRICAL CHARACTERISTICS(1,2,3) (Over Operating Range)

| Symbol | Parameter              | Test Conditions                  | Min. | Max.      | Unit |

|--------|------------------------|----------------------------------|------|-----------|------|

| Vон    | Output HIGH Voltage    | $Vcc$ = Min., Ioн = $-400 \mu A$ | 2.4  | _         | V    |

| Vol    | Output LOW Voltage     | Vcc = Min., IoL = 2.1 mA         | _    | 0.45      | V    |

| VIH    | Input HIGH Voltage(4)  |                                  | 2.0  | Vcc + 0.5 | V    |

| VIL    | Input LOW Voltage(4)   |                                  | -0.5 | 0.8       | V    |

| lu     | Input Load Current     | VIN = 0V to +Vcc                 | _    | 5.0       | μΑ   |

| ILO    | Output Leakage Current | Vout = 0V to +Vcc                | _    | 5         | μΑ   |

#### Notes:

- 1. Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP. Never try to force VPP LOW to 1V below Vcc. Manufacturer suggests to tie VPP and Vcc together during the READ operation.

- 2. Caution: the IS27C020 must not be removed from (or inserted into) a socket when Vcc or VPP is applied.

- 3. Minimum DC input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 10 ns. Maximum DC voltage on output pins is Vcc + 0.5V which may overshoot to Vcc + 2.0V for periods less than 10 ns.

- 4. Tested under static DC conditions.

## POWER SUPPLY CHARACTERISTICS<sup>(1,2,5)</sup> (Over Operating Range)

| Symbol | Parameter                                      | Test Conditions                                                                                                                             | Min. | Max.     | Unit |

|--------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|

| Icc1   | Vcc Operating<br>Supply Current <sup>(3)</sup> | $Vcc = Max., \overline{CE} = Vll$ Commercial $Iout = 0$ mA, $f = 10$ MHz Industrial (Open outputs)                                          | _    | 30<br>60 | mA   |

| IPP1   | VPP Current During<br>Read <sup>(4)</sup>      | $Vcc = Max., \overline{CE} = \overline{OE} = VlL$<br>Vpp = Vcc                                                                              | _    | 100      | μА   |

| IccsB0 | Vcc CMOS Standby<br>Current                    | $\overline{\text{CE}} \ge \text{Vcc} - 0.3\text{V}$<br>All pins $\ge \text{Vcc} - 0.3\text{V}$ or $\le 0.3\text{V}$ toggling f $\le 10$ MHz | _    | 100      | μА   |

| IccsB1 | Vcc TTL Standby<br>Current                     | $\overline{\text{CE}}$ ≥ VIH All pins = VIH or VIL (TTL Level) toggling f ≤ 10 MHz                                                          | _    | 1.0      | mA   |

#### Notes:

- Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP. Never try to force VPP LOW to 1V below Vcc. Manufacturer suggests to tie VPP and Vcc together during the READ operation.

- 2. Caution: the IS27C020 must not be removed from (or inserted into) a socket when Vcc or VPP is applied.

- 3. Icc1 is tested with  $\overline{OE} = V_{IH}$  to simulate open outputs.

- 4. Maximum active power usage is the sum of lcc and lpp.

- 5. Minimum DC input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 10 ns. Maximum DC voltage on output pins is Vcc + 0.5V which may overshoot to Vcc + 2.0V for periods less than 10 ns.

## CAPACITANCE(1,2,3)

|        |                           |            | D    | IP   | PL   | .cc  | TS   | ОР   |      |

|--------|---------------------------|------------|------|------|------|------|------|------|------|

| Symbol | Parameter                 | Conditions | Тур. | Max. | Тур. | Max. | Тур. | Max. | Unit |

| Cin    | Address Input Capacitance | VIN = 0V   | 10   | 12   | 8    | 10   | 10   | 12   | pF   |

| Соит   | Output Capacitance        | Vout = 0V  | 12   | 15   | 9    | 12   | 12   | 14   | pF   |

#### Notes:

- 1. Typical values are for nominal supply voltage.

- 2. This parameter is only sampled, but not 100% tested.

- 3. Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz.

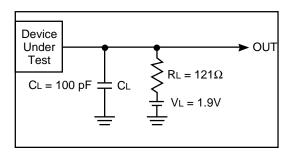

## **SWITCHING TEST CIRCUIT**

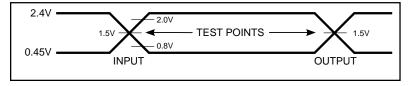

## SWITCHING TEST WAVEFORM

## Notes:

AC Testing:

- 1. Inputs are driven at 2.4V for a logic "1" and 0.45V for a logic "0".

- 2. Input pulse rise and fall skew rate ≥ 1.5V/ns.

## **SWITCHING CHARACTERISTICS**(1,3,4) (Over Operating Range)

| JEDEC           | Std.                       |                                                                                         |                                          | -7   | 70   | -9   | 90   | -1   | 20   |      |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|------|------|------|------|------|------|------|

| Symbol          | Symbol                     | Parameter                                                                               | <b>Test Conditions</b>                   | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| <b>t</b> avqa   | tacc                       | Address to<br>Output Delay                                                              | $\overline{CE} = \overline{OE} = V_{IL}$ | _    | 70   | _    | 90   | _    | 120  | ns   |

| <b>t</b> ELQV   | tce                        | Chip Enable to<br>Output Delay                                                          | ŌĒ = VIL                                 | _    | 70   | _    | 90   | _    | 120  | ns   |

| tGLQV           | toe                        | Output Enable to<br>Output Delay                                                        | CE = VIL                                 | _    | 30   | _    | 35   | _    | 45   | ns   |

| teноz,<br>tgнqz | <b>t</b> DF <sup>(2)</sup> | Chip Enable HIGH or<br>Output Enable HIGH,<br>whichever comes first,<br>to Output Float |                                          | 0    | 20   | 0    | 20   | 0    | 25   | ns   |

| tavox           | tон                        | Output Hold from<br>Address, CE or OE<br>whichever occured first                        |                                          | 0    | _    | 0    | _    | 0    | _    | ns   |

#### Notes:

- 1. Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP.

- 2. This parameter is only sampled, not 100% tested.

- 3. Caution: The IS27C020 must not be removed from (or inserted into) a socket or board when VPP or Vcc applied.

- 4. Output Load: 1 TTL gate and C = CL.

Input Rise and Fall times: 20 ns.

Input Pulse Levels: 0.45 to 2.4V.

Timing Measurement Reference Level: 0.8V nd 2.0V inputs and outputs.

## SWITCHING WAVEFORMS

## Notes:

- 1.  $\overline{OE}$  may be delayed  $\underline{up}$  to  $\underline{tacc}$  toe after the falling edge of  $\overline{CE}$  without impact on tacc. 2.  $\underline{tof}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first.

## **DC PROGRAMMING CHARACTERISTICS**(1,2,3,4) (TA = +25°C $\pm 5$ °C)

| Symbol      | Parameter                         | Test Conditions                            | Min. | Max.      | Unit |

|-------------|-----------------------------------|--------------------------------------------|------|-----------|------|

| Vон         | Output HIGH Voltage During Verify | Іон = –400 μА                              | 2.4  | _         | V    |

| Vol         | Output LOW Voltage During Verify  | IoL = 2.1 mA                               | _    | 0.45      | V    |

| ViH         | Input HIGH Voltage                |                                            | 2.0  | Vcc + 0.5 | V    |

| VIL         | Input LOW Voltage (All Inputs)    |                                            | -0.5 | 0.8       | V    |

| Vн          | A9 Auto Select Voltage            |                                            | 11.5 | 12.5      | V    |

| lu          | Input Current (All Inputs)        | VIN = VIL or VIH                           | _    | 1.0       | μΑ   |

| Icc         | Vcc Supply Current                |                                            | _    | 50        | mA   |

| <b>I</b> PP | VPP Supply Current                | $\overline{CE} = VIL, \overline{OE} = VIH$ | _    | 30        | mA   |

| Vcc         | Supply Voltage                    |                                            | 6.0  | 6.5       | V    |

| VPP         | Programming Voltage               |                                            | 12.5 | 13.0      | V    |

## **SWITCH PROGRAMMING CHARACTERISTICS**(1,2,3,4) (TA = +25°C $\pm$ 5°C)

| JEDEC         | Std.         | Danamatan                     | B#*  | <b>N</b> 4 | 119  |

|---------------|--------------|-------------------------------|------|------------|------|

| Symbol        | Symbol       | Parameter                     | Min. | Max.       | Unit |

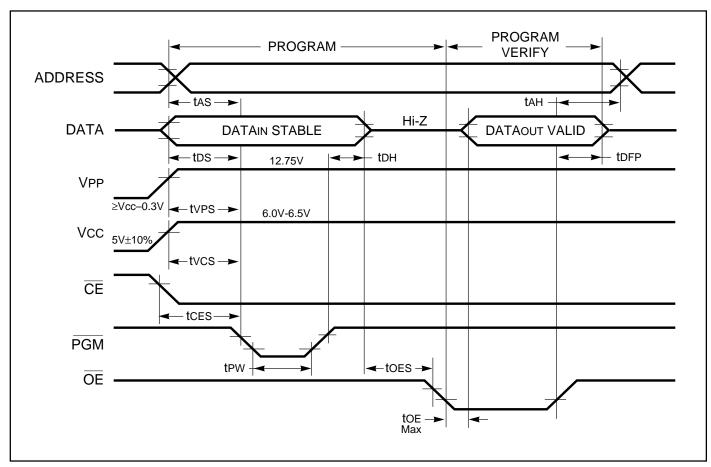

| <b>t</b> AVEL | <b>t</b> as  | Address Setup Time            | 2    | _          | μs   |

| <b>t</b> DZGL | toes         | OE Setup Time                 | 2    | _          | μs   |

| <b>t</b> DVEL | tos          | Data Setup Time               | 2    |            | μs   |

| <b>t</b> GHAX | <b>t</b> AH  | Address Hold Time             | 0    | _          | μs   |

| <b>t</b> EHDX | <b>t</b> DH  | Data Hold Time                | 2    | _          | μs   |

| <b>t</b> GHQZ | <b>t</b> DFP | OE HIGH to Output Float Delay | 0    | 130        | ns   |

| tvps          | tvps         | VPP Setup Time                | 2    | _          | μs   |

| teleh1        | <b>t</b> PW  | PGM Program Pulse Width       | 95   | 105        | μs   |

| tvcs          | tvcs         | Vcc Setup Time                | 2    | _          | μs   |

| <b>t</b> ELPL | tces         | CE Setup Time                 | 2    | _          | μs   |

| <b>t</b> GLQV | <b>t</b> oe  | Data Valid from OE            | _    | 150        | ns   |

## Notes:

- 1. Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP.

- 2. VPP must be  $\geq$  Vcc during the entire programming and verifying procedure.

- 3. When programming IS27C020, a 0.1 μF capacitor is required across VPP and ground to suppress spurious voltage transients which may damage the device.

- 4. Programming characteristics are sampled but not 100% tested at worst-case conditions.

## PROGRAMMING ALGORITHM WAVEFORM(1,2)

#### Notes

- 1. The timing reference level is 1.5V for inputs and outputs.

- 2. toe and toep are characteristics of the device but must be accommodated by the programmer.

## PROGRAMMING FLOW CHART

## **ORDERING INFORMATION**

Commercial Range: 0°C to +70°C

| Speed (ns) | Order Part Number | Package                            |

|------------|-------------------|------------------------------------|

| 70         | IS27C020-70W      | 600-mil Plastic DIP                |

| 70         | IS27C020-70PL     | PLCC – Plastic Leaded Chip Carrier |

| 70         | IS27C020-70T      | TSOP                               |

| 90         | IS27C020-90W      | 600-mil Plastic DIP                |

| 90         | IS27C020-90PL     | PLCC – Plastic Leaded Chip Carrier |

| 90         | IS27C020-90T      | TSOP                               |

| 120        | IS27C020-12W      | 600-mil Plastic DIP                |

| 120        | IS27C020-12PL     | PLCC - Plastic Leaded Chip Carrier |

| 120        | IS27C020-12T      | TSOP                               |

## **ORDERING INFORMATION**

Industrial Range: -40°C to +85°C

| Speed (ns) | Order Part Number | Package                            |

|------------|-------------------|------------------------------------|

| 70         | IS27C020-70W      | 600-mil Plastic DIP                |

| 70         | IS27C020-70PL     | PLCC - Plastic Leaded Chip Carrier |

| 70         | IS27C020-70T      | TSOP                               |

| 90         | IS27C020-90W      | 600-mil Plastic DIP                |

| 90         | IS27C020-90PL     | PLCC – Plastic Leaded Chip Carrier |

| 90         | IS27C020-90T      | TSOP                               |

| 120        | IS27C020-12W      | 600-mil Plastic DIP                |

| 120        | IS27C020-12PL     | PLCC – Plastic Leaded Chip Carrier |

| 120        | IS27C020-12T      | TSOP                               |

# Integrated Silicon Solution, Inc.

680 Almanor Avenue Sunnyvale, CA 94086 Tel: (408) 733-4774

Fax: (408) 245-4774

Tool Free: 1-800-379-4774 http://www.issiusa.com